## Hugh Chesser, CSEB 1012U

| -               | AD           | K ]           |        | 41 S 11 -   | 0 8/ - 1 = |       | ୍ର ରାଷ   | <b>N A B</b>                 |

|-----------------|--------------|---------------|--------|-------------|------------|-------|----------|------------------------------|

| 8 I<br>5<br>0 T | M U K<br>W D | 社明を           | I<br>S |             | 文権なりて、     |       | -        |                              |

| HER             | а – п<br>19  | がある           | Y H E  | NAG<br>HHAG |            |       |          | 学 Y と                        |

| E               | NE           | 字<br>印 ><br>び | M A    |             |            |       | CRE N SE | び<br>to<br>to<br>N<br>H<br>技 |

| B H<br>B E      | 0 I<br>A T   | 技す回           | 5 18   |             |            |       | V        | V10-M                        |

| 5               | NH           | 王 (           | 8      |             | E 1        | 2 H H |          |                              |

CSE

# Agenda

Topics:

1. Multiple cycle implementation - complete

Patterson: Appendix C, D

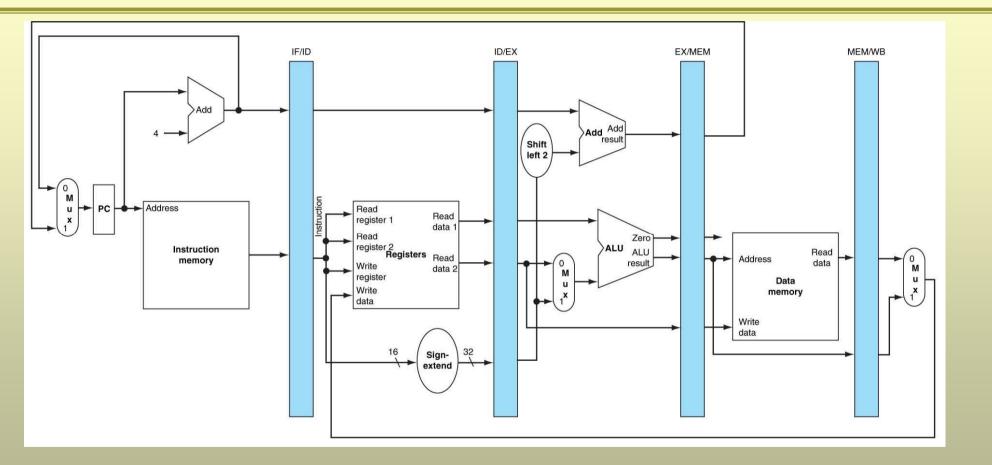

## **Breaking the Instruction Execution into Clock Cycles**

Execution of each instruction is broken into a series of steps

- Each step is balanced to do almost equal amount of work

- Each step takes one clock cycle

- Each step contains at the most 1 ALU operation, or 1 register file access, or 1 memory access

- Operations listed in 1 step occurs in parallel in 1 clock cycle

- Different steps occur in different clock cycles

- Different steps are:

- 1. IF: Instruction fetch step

- 2. ID: Instruction decode and register fetch step

- 3. EX: Execution, memory address computation, or branch completion step

- 4. MEM: Memory access of R-type instruction completion step

- 5. WB: Write back completion step

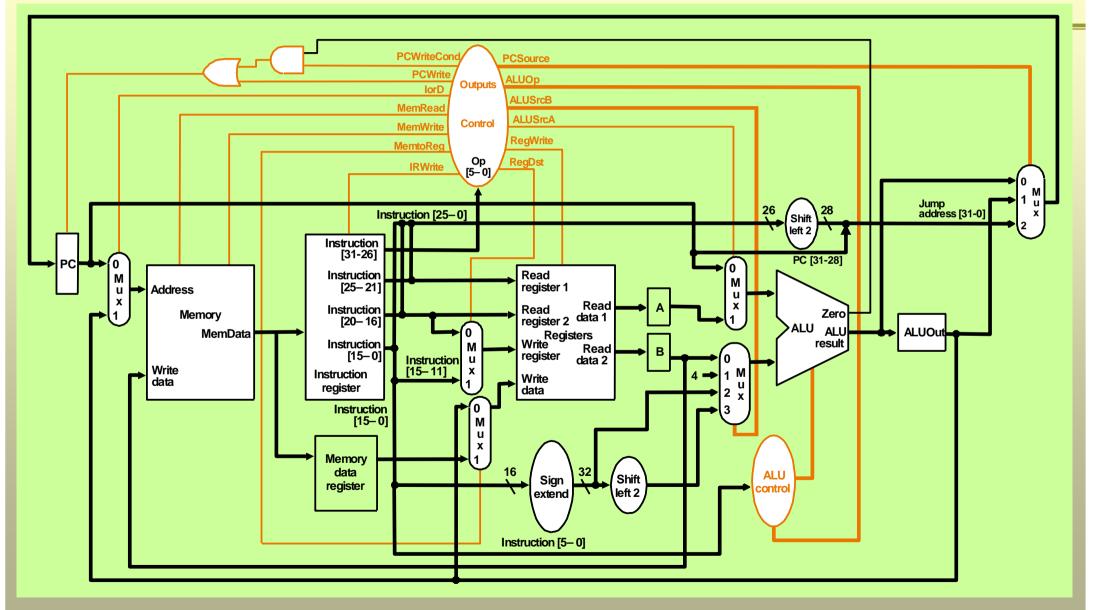

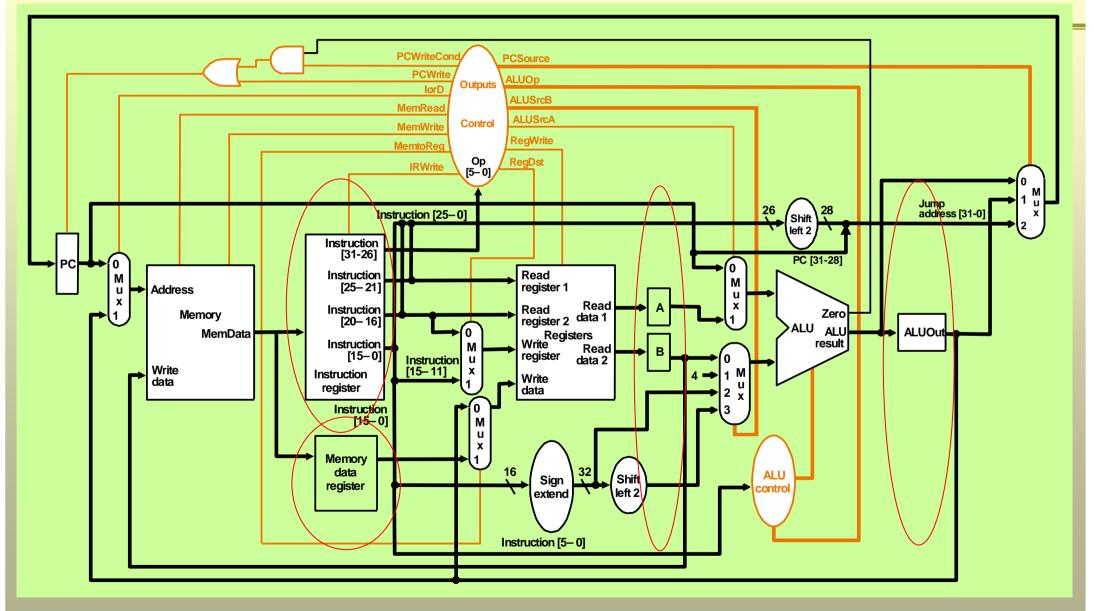

#### **Multicycle Implementation: Control Units added**

## **Multicycle Implementation – 5 Steps**

Multicycle implementation – "unwound" to show datapath in each step

#### **Summary of Steps used in different Instructions**

|                                                               | Action for                                                                                                 |                                                                           |                                         |                                    |  |  |  |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------|------------------------------------|--|--|--|

| Step Name                                                     | <b>R-type Instruction</b>                                                                                  | Memory Reference<br>Instruction                                           | Branch                                  | Jump                               |  |  |  |

| <b>IF</b> - Instruction<br>fetch                              | <pre>IR = Memory[PC]; PC = PC + 4;</pre>                                                                   |                                                                           |                                         |                                    |  |  |  |

| ID - Instruction<br>decode /<br>Register fetch                | <pre>A = Reg[IR[25-21]];<br/>B = Reg[IR[20-16]];<br/>ALUOut = PC + (sign-extend(IR[15-0])&lt;&lt;2);</pre> |                                                                           |                                         |                                    |  |  |  |

| EX –<br>R-type Execution /<br>address comp. /<br>Branch /Jump | ALUOut=A op B                                                                                              | ALUOut = A + sign-<br>extend(IR[15-0])                                    | <pre>if(A == B) then PC = ALUOut;</pre> | PC = PC[31-28]  <br>(IR[25-0)<<2); |  |  |  |

| MEM - Memory<br>Access /<br>R-type Completion                 | Reg[IR[15-11]]<br>= ALUOut;                                                                                | <pre>lw:<br/>MDR = Memory[ALUOut]<br/>or sw:<br/>Memory[ALUOut] = B</pre> |                                         |                                    |  |  |  |

| WB - Memory Read<br>Completion                                |                                                                                                            | lw:<br>Reg[IR[20-16]]=MDR;                                                |                                         | 6                                  |  |  |  |

7

- Recall that design of single cycle datapath was based on a combinational circuit

- Design of multicycle datapath is more complicated

- 1. Instructions are executed in a series of steps

- 2. Each step must occur in a sequence

- 3. Control of multicycle must specify both the control signals and the next step

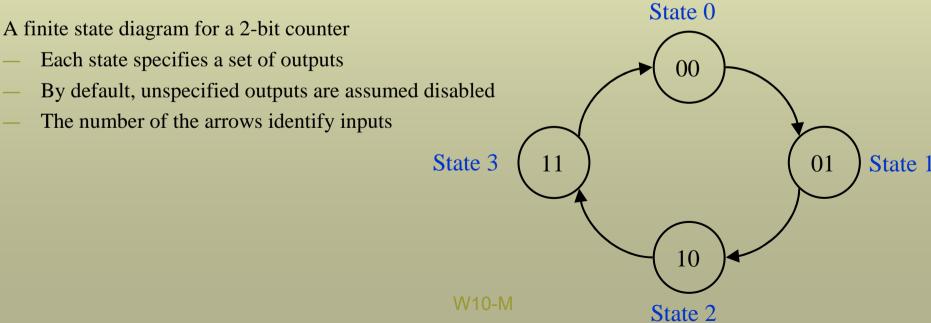

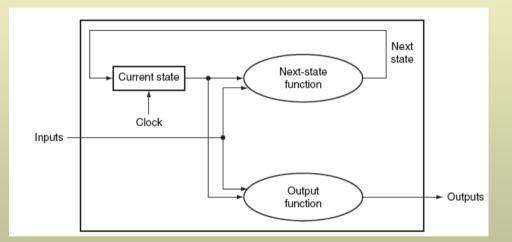

- The control of a multicycle datapath is based on a sequential circuit referred to as a finite state machine

# **Finite State Machine?**

#### • See Appendix C

- A sequential logic function which has a state and inputs – the logic function determines the next state and outputs

- Moore machine outputs depend on just the current state

- Mealy machine outputs depend on current state and inputs

- Book uses Moore machine description

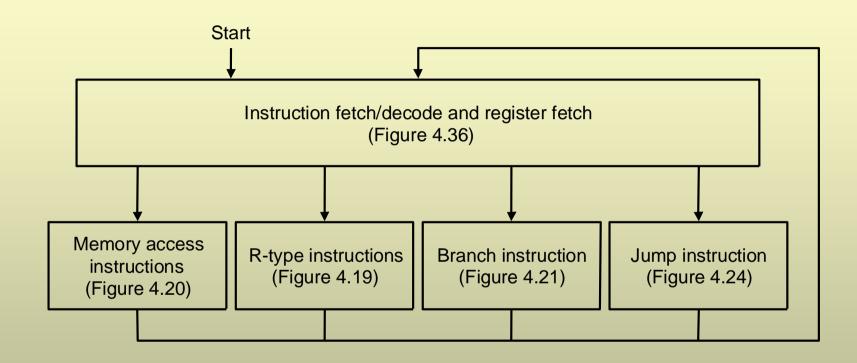

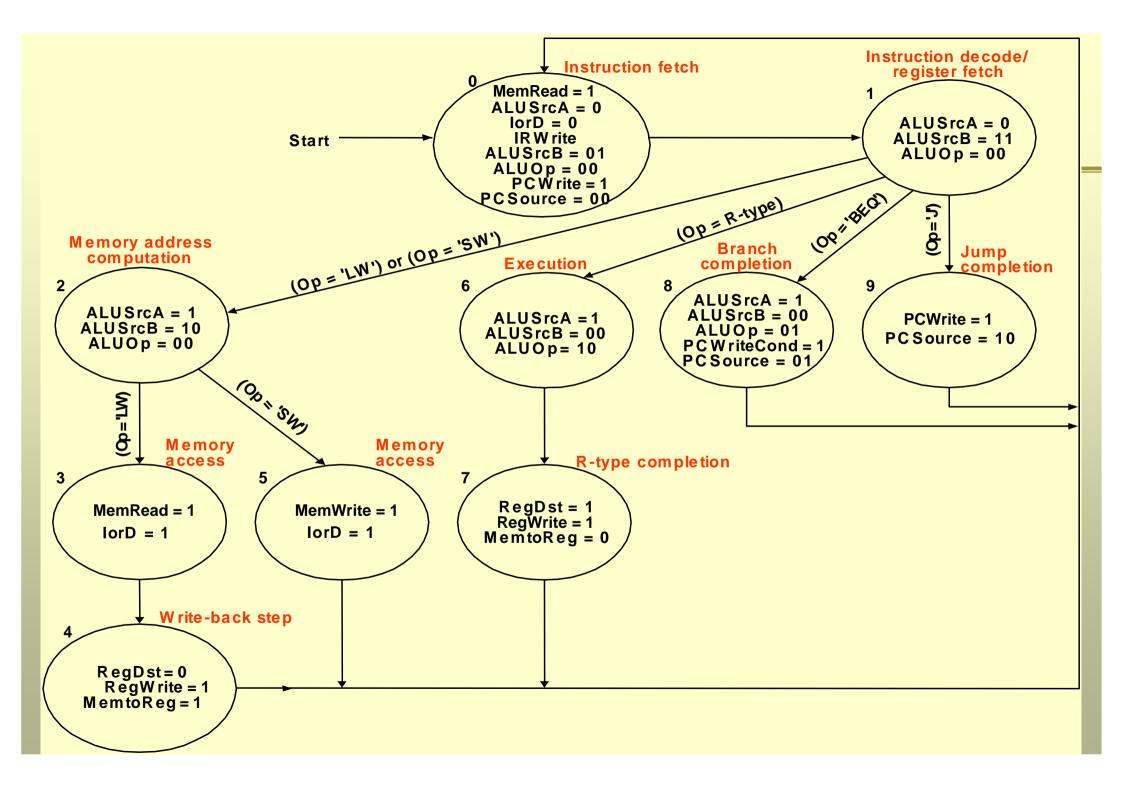

## Finite State Machine Control of Multicycle Datapath (1)

High-Level View

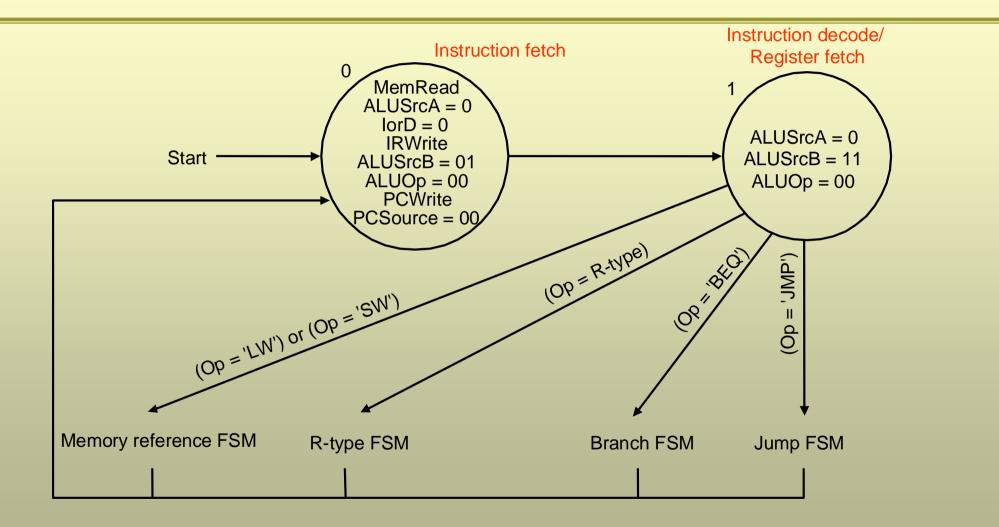

### **Finite State Machine Control of Multicycle Datapath (2)**

Fig. D.3.1: Steps 1 and 2: Instruction Fetch and Decode Instructions

W10-M

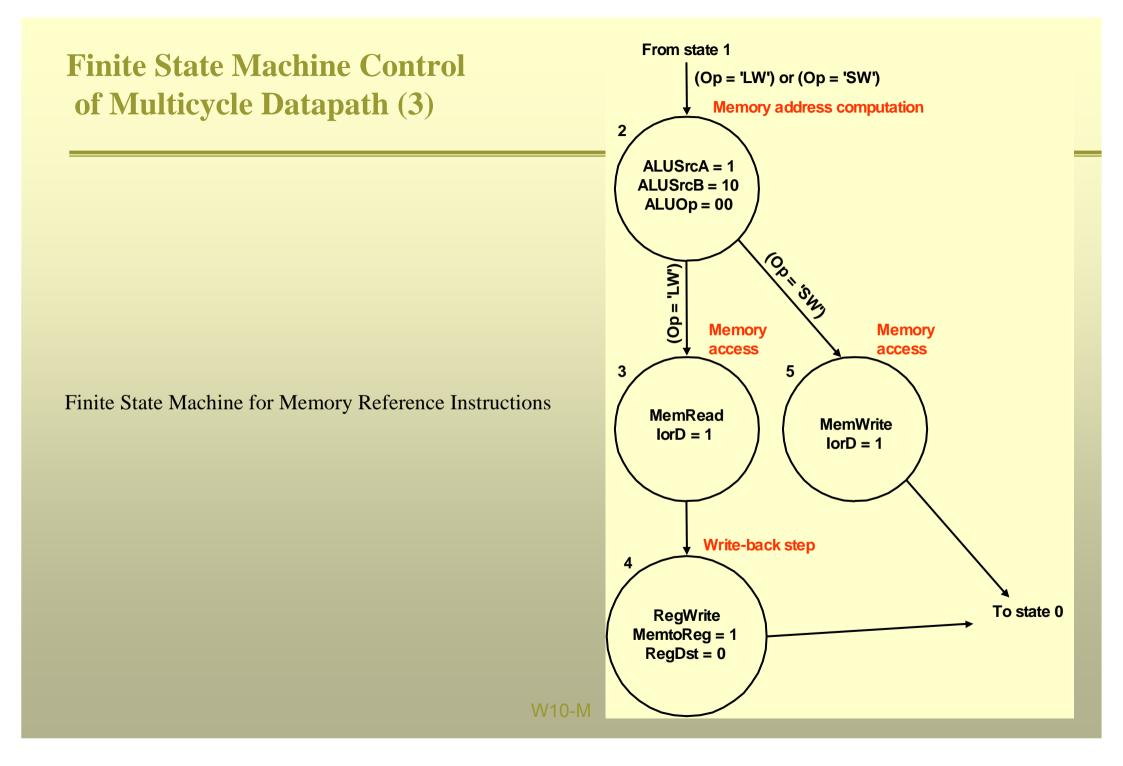

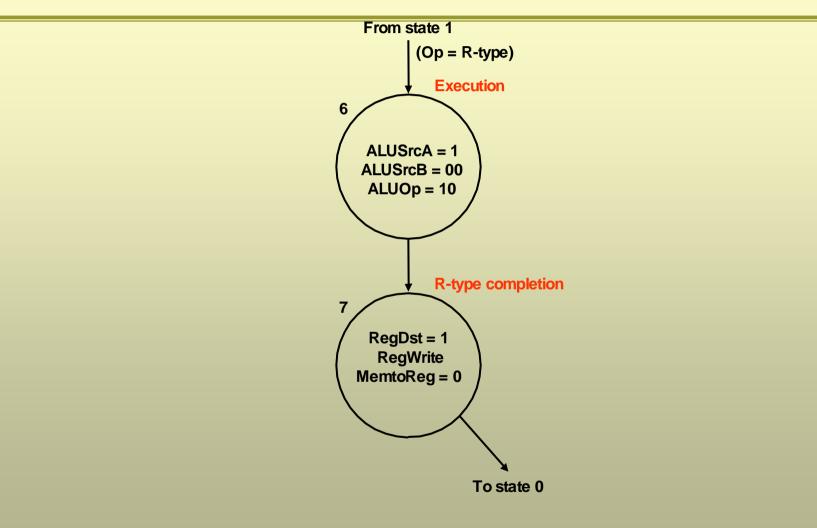

### **Finite State Machine Control of Multicycle Datapath (4)**

Finite State Machines for R-type Instructions

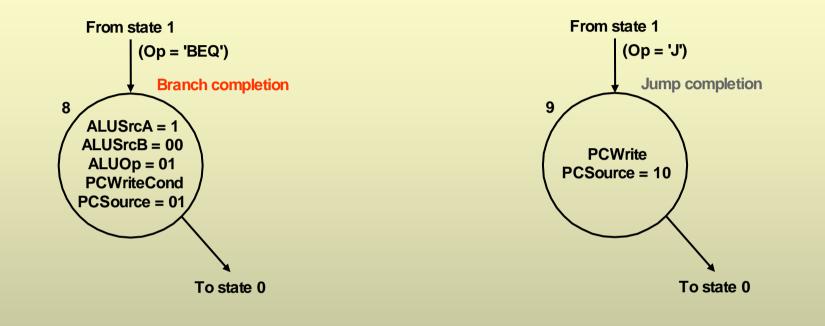

### **Finite State Machine Control of Multicycle Datapath (5)**

Finite State Machine for Branch Instruction

Finite State Machine for Jump Instruction

#### **Finite State Machine** Control of Multicycle Datapath (5)

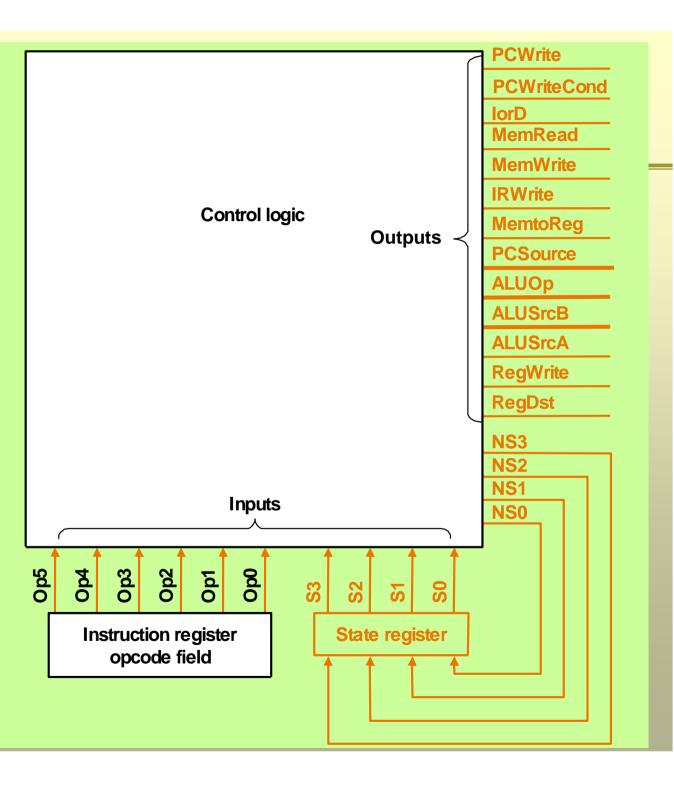

# **Control Logic – Truth Table**

Note that control outputs depend only on current state (Op column is blank for all output rows)

Next state depends on current state and inputs (opcode from instruction)

| Output      | Current states                             | Ор                        |

|-------------|--------------------------------------------|---------------------------|

| PCWrite     | state0 + state9                            |                           |

| PCWriteCond | state8                                     |                           |

| lorD        | state3 + state5                            |                           |

| MemRead     | state0 + state3                            |                           |

| MemWrite    | state5                                     |                           |

| IRWrite     | state0                                     |                           |

| MemtoReg    | state4                                     |                           |

| PCSource1   | state9                                     |                           |

| PCSource0   | state8                                     |                           |

| ALUOp1      | state6                                     |                           |

| ALUOp0      | state8                                     |                           |

| ALUSrcB1    | state1 +state2                             |                           |

| ALUSrcB0    | state0 + state1                            |                           |

| ALUSrcA     | state2 + state6 + state8                   |                           |

| RegWrite    | state4 + state7                            |                           |

| RegDst      | state7                                     |                           |

| NextState0  | state4 + state5 + state7 + state8 + state9 |                           |

| NextState1  | state0                                     |                           |

| NextState2  | state1                                     | (Op = '1w') + (Op = 'sw') |

| NextState3  | state2                                     | (Op = '1w')               |

| NextState4  | state3                                     |                           |

| NextState5  | state2                                     | (Op = 'sw')               |

| NextState6  | state1                                     | (Op = 'R-type')           |

| NextState7  | state6                                     |                           |

| NextState8  | state1                                     | (Op = 'beq')              |

| NextState9  | state1                                     | (Op = 'jmp')              |

#### **Multicycle Implementation: Control Units added**