# Hugh Chesser, CSEB 1012U

| 1002420 |    | - 6 |      |    |     |   | 60         | -    |         | -          | 10-10  | <u></u> | -    |         |        |      | <u> </u> |        |     | W.  | 10 |

|---------|----|-----|------|----|-----|---|------------|------|---------|------------|--------|---------|------|---------|--------|------|----------|--------|-----|-----|----|

| Т       | 14 |     | 1    | 1  | 문   |   |            | -    | N E     | 00         | 9      | X       | 5    |         |        | 100  |          |        | E   | H · |    |

| I       | 14 |     | 71   | ×. | 8   |   | 0 44       | 86   | 2 OII   | 文          | Stat   |         | eth. | CERS    | 社      | 10   | 2        | 100    | 5   |     |    |

| 10      |    |     | PHER |    |     |   | 12         | 5    |         | - <b>1</b> |        | 72 11   | σ.   | HAV     | 间 T    | - 68 | N =      | -7.2   | E   | 2   | 老  |

| T       | 0  | Ш   | 1    |    | 5   |   |            |      | I.A.    | 4          | aler 1 |         | 授    | 1.2     | KC     | 1    | 12 2     | C 2    | W D |     | 12 |

|         |    |     | 62   | *  |     |   |            | - 65 | TO N    | 2          |        | 1 1     | 9    | T WITH  | 3      |      | 0        | -m     | 1 1 |     |    |

| E       |    | U.  | 美    | ä  |     | Ħ | цц.<br>(Д. |      | I A     | E.         |        | 3       | 100  | 2 32    | 10     | 16   |          |        | 5   | 1   | G  |

| 2       | D  | 5   | 5    |    | H.  |   | 2          |      | 5 G     | ÷1         |        |         |      | 1 25    | 2      |      |          | in the |     | P   | 7  |

|         |    |     | 字    |    | 8   |   |            | 0    | - E     | 明          |        | R 1     |      | 5 200   |        |      | A        | ੇ ਹਾ   | 0   | u   | 甲了 |

|         |    | 1   | 印    | 2  | 59- | M | DU         | -    | FIL NUL | 5          |        | T       |      | 5       | 35 114 | S.C  | N 21     | 技      |     |     | TF |

|         |    | Ŧ   | 28   |    |     | A | 팘          | 1    | 444     | を          |        | 1       |      | a 👘     | ED     |      | A        | 8.2    |     | M S | 技  |

|         | Ø  | I   | 48   | 12 |     |   |            |      | 2       | 1          |        | P 5     |      | E I B A | U      |      | G        |        |     | ACC | 31 |

|         |    | 5   | f    |    |     |   | -16        |      | 2.      | 2          |        | Ŧ       |      | S S 👙   | 8      |      |          |        |     |     |    |

|         | A  | T   | 100  |    |     |   |            |      | - I     | -          |        |         |      | - E     | N.     |      |          | W8-I   | M   |     |    |

|         | 13 | -   | 104  | 20 | 8   |   | 18         | p.   | A RI    | 王          |        |         |      | 0 Y 1   |        |      |          |        |     |     |    |

|         |    |     | 프    |    |     |   |            | 0.5  | MOL.    | HP.        |        |         |      | 2 H     | 244    | -    |          |        |     |     | 2  |

CSE

# **Schedule, Reminders**

Make-up Labs

•Complete Labs A – D

No

additional

"Lab X"

| WEEK OF | Mon | Wed                  | Lab          | Торіс                             |

|---------|-----|----------------------|--------------|-----------------------------------|

| Sep 07  | -   |                      | -            | Overview of the course            |

| Sep 14  |     |                      | -            | Performance and Data Translation  |

| Sep 21  |     |                      | А            | Code Translation                  |

| Sep 28  |     | Quiz #1              | В            | Translating Utility Classes       |

| Oct 05  |     |                      | С            | Translating Objects               |

| Oct 12  | -   | -                    | -            | READING WEEK - No Classes         |

| Oct 19  |     | Mid-term in TEL 0014 | D            | Introduction to Hardware          |

| Oct 26  |     |                      | Make-up Labs | Machine Language + Floating-Point |

| Nov 02  |     |                      | K            | The CPU Datapath                  |

| Nov 09  |     | Quiz #2              | L            | The Single-Cycle Control          |

| Nov 16  |     |                      | М            | Pipelining                        |

| Nov 23  |     |                      | N            | Caches                            |

| Nov 30  |     | Quiz #3              | Make-up Labs |                                   |

| Dec 07  |     | -                    | -            | No lecture on Wednesday           |

#### H/W CSE 2821 0/S S/W

# Agenda

# Topics:

- Register files, Decoder, Data Memory, Instruction Memory – Building Blocks

- 2. Complete hardware implementation of goal instructions

Patterson: Appendix C, Section 4.1, 4.2, 4.3

#### **Overview** (1)

Goal: Implement a subset of core instructions from the MIPS instruction set, given below

| Category      | Instruction        | Example            | Meaning                               | Comments |

|---------------|--------------------|--------------------|---------------------------------------|----------|

|               | add                | add \$s1,\$s2,\$s3 | \$s1 ← \$s2+\$s3                      |          |

|               | subtract           | sub \$s1,\$s2,\$s3 | \$s1 ← \$s2-\$s3                      |          |

| Arithmetic    | and                | add \$s1,\$s2,\$s3 | \$s1 ← \$s2&\$s3                      | & => and |

| and Logical   | or                 | or \$s1,\$s2,\$s3  | \$s1 ← \$s2 \$s3                      | => or    |

|               | slt                | slt \$s1,\$s2,\$s3 | If \$s1 < \$s3, \$s1←1<br>else \$s1←0 |          |

| Dete Trensfor | load word          | lw \$s1,100(\$s2)  | \$s1 ← Mem[\$s2+100]                  |          |

| Data Transfer | store word         | sw \$s1,100(\$s2)  | Mem[\$s2+100] ← \$s1                  |          |

| Branch        | branch on equal    | beq \$s1,\$s2,L    | if(\$s1==\$s2) go to L                |          |

| Dranch        | unconditional jump | j 2500             | go to 10000                           |          |

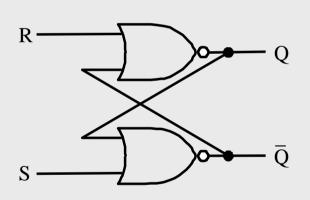

## **Basics: RS Latch (3)**

Simplest memory elements are Flip-flops and Latches

- In clocked latches, state changes whenever input changes and the clock is asserted.

- In flip-flops, state changes only at the trailing edge of the clock

| Inp | outs | Out | puts               | Comments                |  |  |  |

|-----|------|-----|--------------------|-------------------------|--|--|--|

| S   | R    | Q   | $\bar{\mathbf{Q}}$ |                         |  |  |  |

|     |      | 0   | 1                  | Initial Condition       |  |  |  |

| 1   | 0    | 1   | 0                  |                         |  |  |  |

| 0   | 0    | 1   | 0                  | After $S = 1$ , $R = 0$ |  |  |  |

| 0   | 1    | 0   | 1                  |                         |  |  |  |

| 0   | 0    | 0   | 1                  | After $S = 0, R = 1$    |  |  |  |

| 1   | 1    | 0   | 0                  | Undefined               |  |  |  |

Logic Diagram

Function Table

RS Unclocked Latch

— For a RS-latch: output Q = 1 when S = 1, R = 0 (set condition) output Q = 0 when S = 0,  $R^{HB-M} = 1$  (reset condition)

5

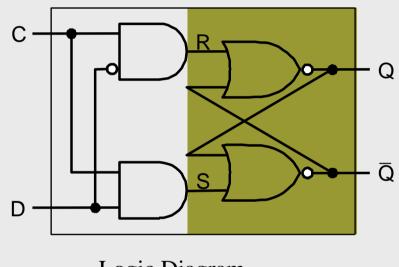

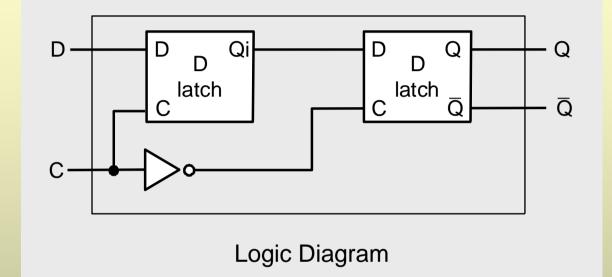

## **Basics: Clocked D Latch (4)**

1. For a D-latch: output Q = 1 when D = 1 (set condition) output Q = 0 when D = 0 (reset condition)

| Inp | outs | Out   | puts  | Comments |  |  |  |  |

|-----|------|-------|-------|----------|--|--|--|--|

| С   | D    | Q Q   |       |          |  |  |  |  |

| 0   | Х    | Uncha | anged |          |  |  |  |  |

| 1   | 0    | 0 1   |       | Reset    |  |  |  |  |

| 1   | 1    | 1 0   |       | Set      |  |  |  |  |

Logic Diagram

2. D Latch requires clock to be asserted for output to change

6

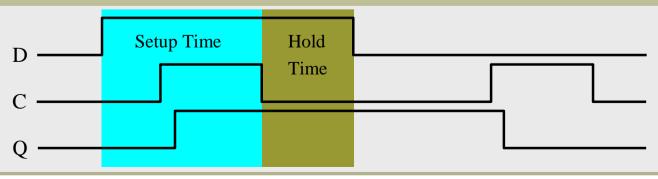

# **Basics: Falling Edge Triggered D flip-flop (5)**

Output Q follows D but changes only at the falling edge

7

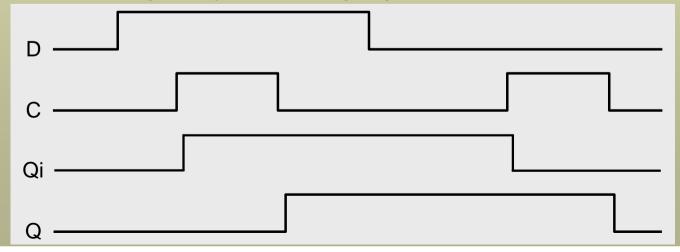

#### **Basics: 32-bit Registers (6)**

Falling edge triggered D flip-flops can be combined to form a register

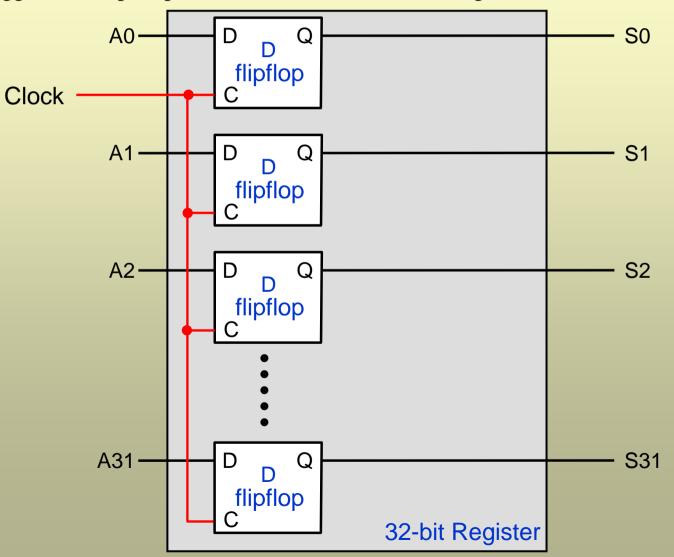

#### **Basics: Register Files (6)**

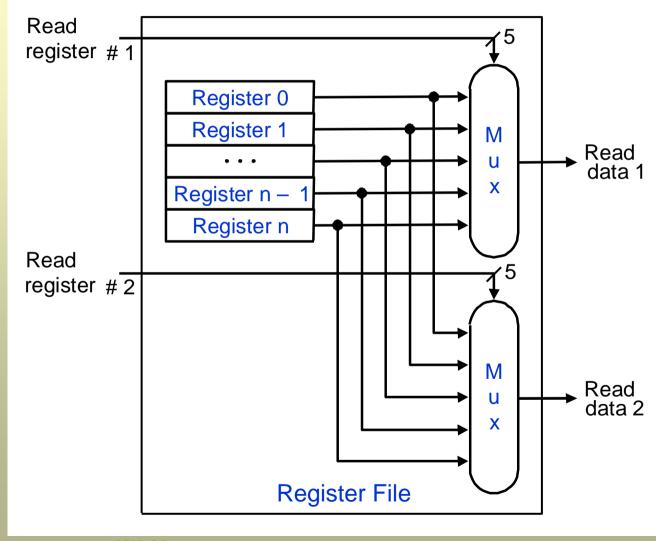

- 1. Register files consist of a set of registers that can be read or written individually

- 2. In MIPS, register file contains 32 registers

- 3. Two registers can be read simultaneously

- 4. One register can be written at one time

# **Basics: Read Operation in Register Files (7)**

Read Operation:

- Register number of the register to be read is provided as input

- Content of the read register is the output of the register file

- Multiplexers are used in the read operation

**W8-M**

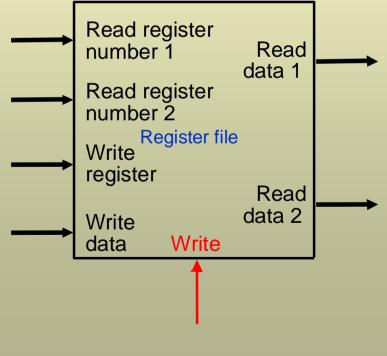

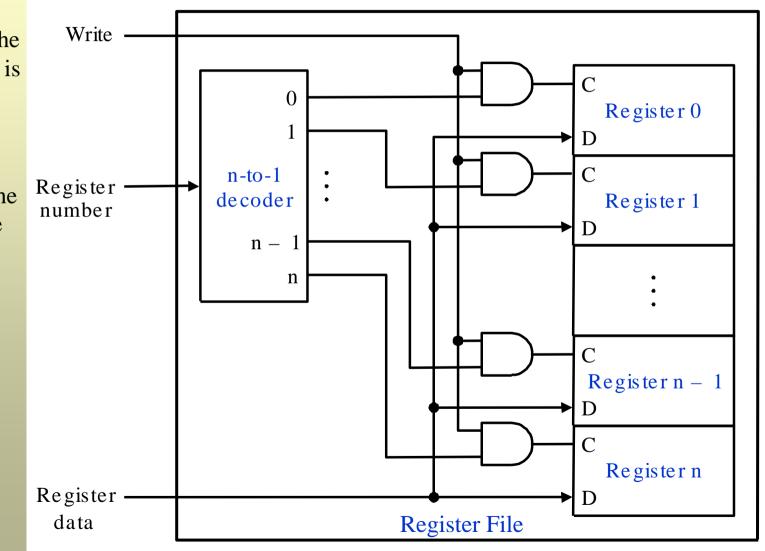

# **Basics: Write Operation in Register Files (8)**

Write Operation:

- Register number of the register to be written is one input

- Data to be written is the second input

- Clock that controls the write operation is the third input

- Decoders are used in the write operation

|                                           |     | Inputs |     |      | Outputs |      |      |      |      |      |      |  |

|-------------------------------------------|-----|--------|-----|------|---------|------|------|------|------|------|------|--|

| What is a Decoder?                        | In2 | ln1    | In0 | Out7 | Out6    | Out5 | Out4 | Out3 | Out2 | Out1 | Out0 |  |

| Out0                                      | 0   | 0      | 0   | 0    | 0       | 0    | 0    | 0    | 0    | 0    | 1    |  |

| → Out1                                    | 0   | 0      | 1   | 0    | 0       | 0    | 0    | 0    | 0    | 1    | 0    |  |

| → Out2                                    | 0   | 1      | 0   | 0    | 0       | 0    | 0    | 0    | 1    | 0    | 0    |  |

| $\xrightarrow{3}$ Decoder $$ Out3<br>Out4 | 0   | 1      | 1   | 0    | 0       | 0    | 0    | 1    | 0    | 0    | 0    |  |

| → Out5                                    | 1   | 0      | 0   | 0    | 0       | 0    | 1    | 0    | 0    | 0    | 0    |  |

| → Out6                                    | 1   | 0      | 1   | 0    | 0       | 1    | 0    | 0    | 0    | 0    | 0    |  |

| Out7                                      | 1   | 1      | 0   | 0    | 1       | 0    | 0    | 0    | 0    | 0    | 0    |  |

| 3-bit Decoder                             | 1   | 1      | 1   | 1    | 0       | 0    | 0    | 0    | 0    | 0    | 0    |  |

# **Basics: Write Operation in Register Files (9)**

Write Operation:

- Register number of the register to be written is one input

- Data to be written is the second input

- Clock that controls the write operation is the third input

- Decoders are used in the write operation

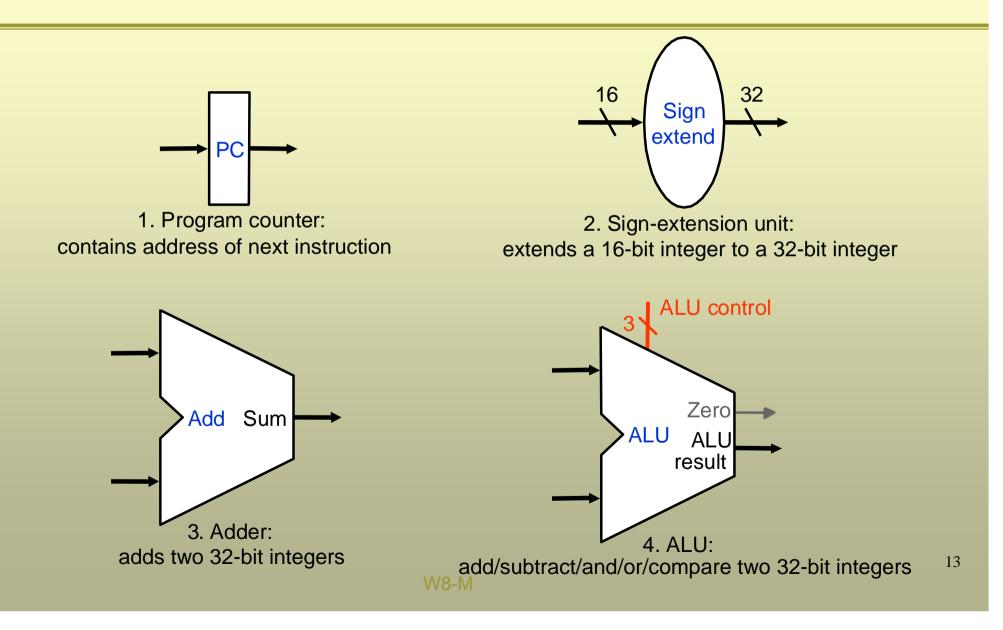

#### **Basic Building Blocks (1)**

#### **Basic Building Blocks (2)**

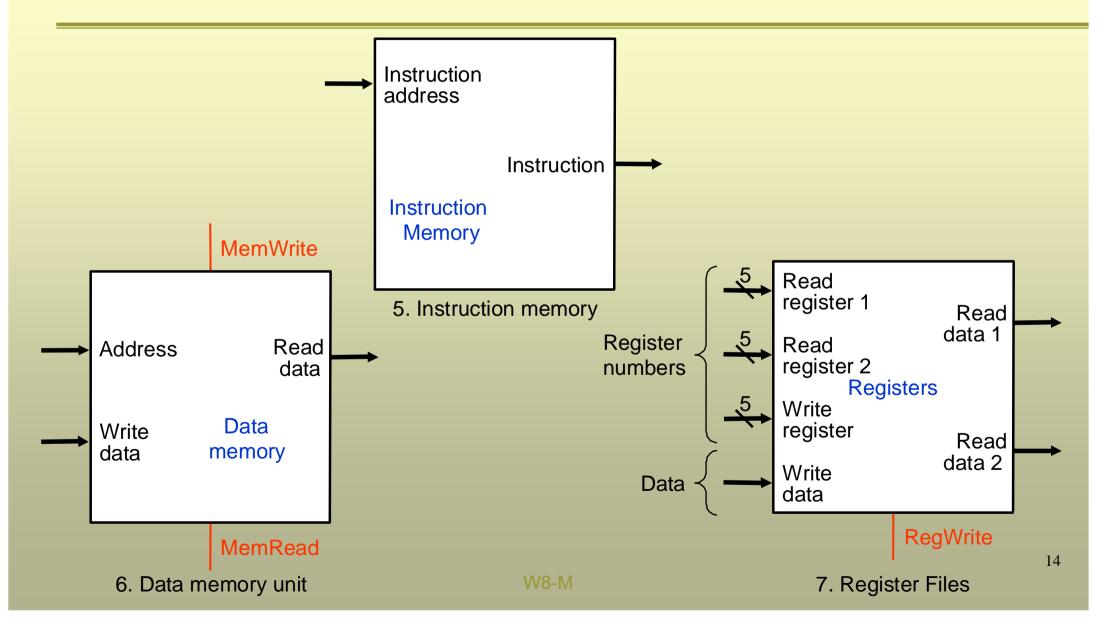

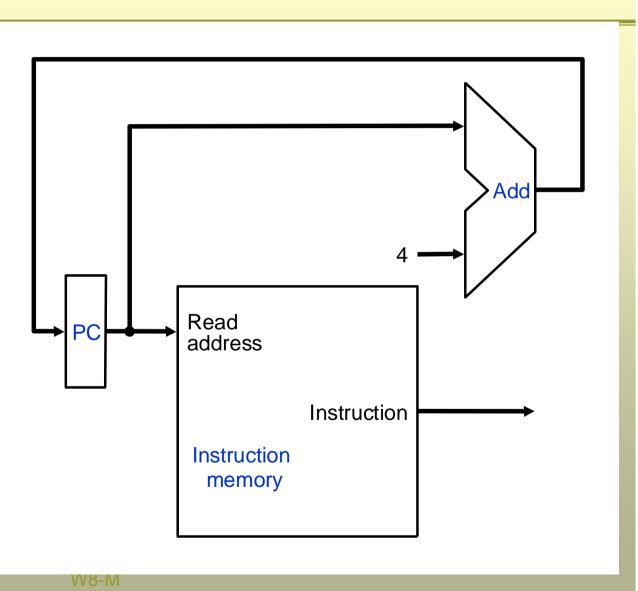

# **Datapath: Fetch Instruction**

- 1. Provide address from PC to Instruction Memory

- 2. Increment PC by 1 word (4 bytes)

- 3. Fetch the instruction

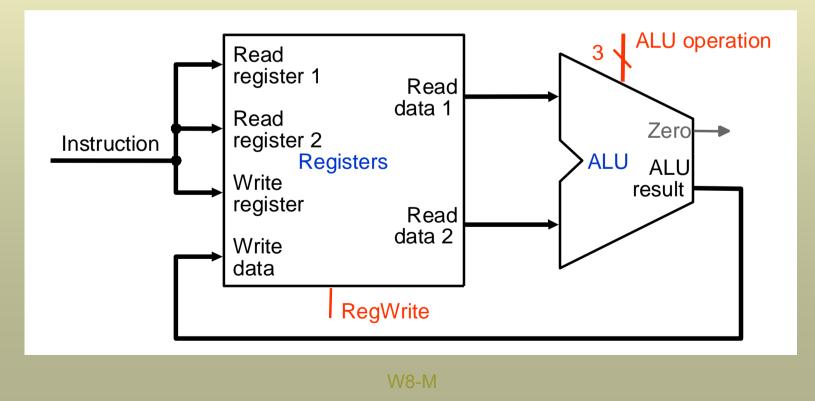

### **Datapath: R-type Instructions**

R-type instructions include arithmetic and logical instructions (add, sub, or, and, slt) Example: add \$\$1,\$\$2,\$\$3

- 1. Read two registers (\$s2,\$s3) specified in the instruction

- 2. ALU performs the required operation (add) on the two operands

- 3. Output of ALU is written to the specified register (\$s1)

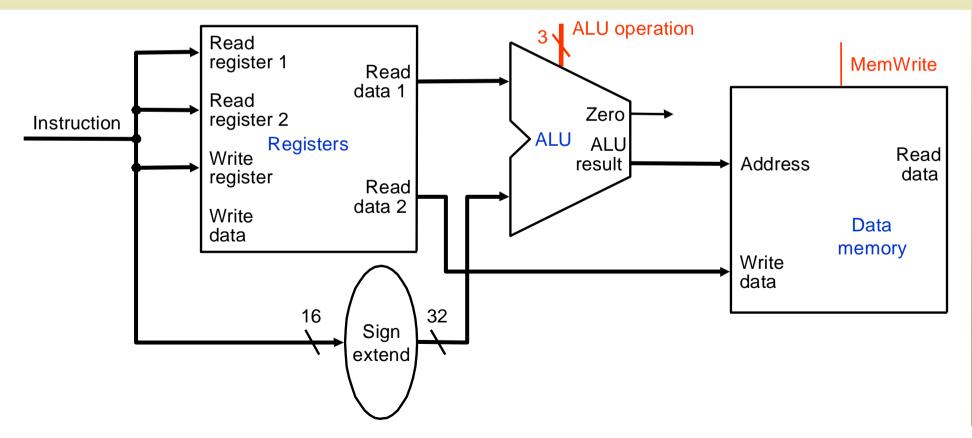

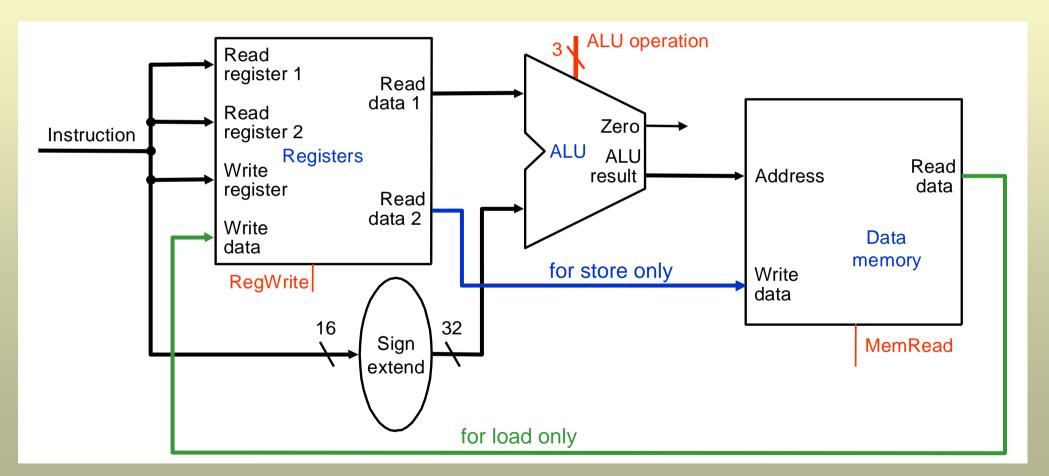

#### **Datapath: Data transfer Instruction (1)**

17

#### Store instruction sw \$s1,offset(\$s2)

- 1. Read two registers (\$s1,\$s2) specified in the instruction.

- 2. Offset is extended to 32 bits.

- 3. ALU adds offset with specified register (\$s2) to obtain data memory address.

- 4. Address along with data of the register (\$s1) to be stored passed to data memory.

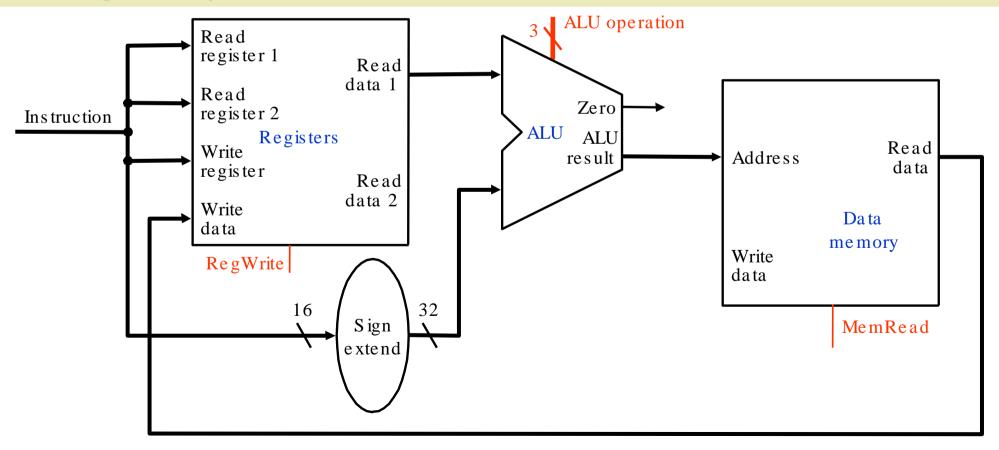

# **Datapath: Data transfer Instruction (2)**

Load instruction lw \$s1,offset(\$s2)

- 1. Read register (\$s2) specified in the instruction. 2. Offset is extended to 32 bits.

- 3. ALU adds offset with specified register (\$s2) to obtain data memory address.

- 4. Data memory transfers data from provided address to Register file where it is stored in the specified register (\$s1).

# **Datapath: Data transfer Instruction (3)**

Load and store instruction combined

# **Datapath: Branch Instructions**

copied to PC

Example: beq \$s1,\$s2,Loop PC + 4 from instruction datapath Compiler translation: Branch Add Sum beq \$s1,\$s2,w offset target #if \$s1==\$s2, goto (PC+4+4\*w offset) Shift Instruction 1. Read two registers left 2 (\$s2,\$s3) specified **ALU** operation Read in the instruction register 1 Read 2. ALU compares data 1 Read register 2 content of specified To branch ALU Zero Registers control logic registers (\$s1,\$s2) Write register Read 3. Adder computes data 2 Write the branch address data 4. If equal (zero = 1), RegWrite branch address is 32 16 Sign extend