# -C-S-E==2021== -C-O-M-FU-T-E-R==-O-R-G-A-N-I-Z-A-T-I-O-N

| ]       |          |              |            |          |            | <br>]  |                   |             |          |    | 3 4 1 4 8 6 美と | Y T<br>V T<br>U T<br>W I | もレ 保の 文頼な | Land Land | REAMWOR<br>REAMWOR |          | の文積なフト社  |          | · 10.810 4 | 一保の文積なフト   |

|---------|----------|--------------|------------|----------|------------|--------|-------------------|-------------|----------|----|----------------|--------------------------|-----------|-----------|--------------------|----------|----------|----------|------------|------------|

| THUTTUR | UT NOK N | ac u = c o   | トな明 やじ笑と 学 | る気を      | きゅう 11 日   | IS YHE | 中 び技す 国出のショ       | A 2147 40 O | の文精なフト社明 |    |                | N I CLANDER PLAN         | フト社開たに美と  | EE407012  | > 0 (ITEN) U T     |          | 明をに美と学印び |          |            | 社会 をに美と 字印 |

|         | NHOKN    | 표 (= H H H H | 印 び抜す 園出   | ∧ 24 A 2 | A 22 40 00 | M A T  | <b>31、</b> 94歳間 3 | 14 H        | をに美と 字印  | 44 |                |                          |           |           | C N<br>G           | 96<br>-w | -5₩      | <b>√</b> |            | び技士        |

D R

## Combinational Logic: Design of a 1-bit adder (2)

Step 2: Derive the Boolean expression for each output from the truth table

| INPUTS | <b>S</b> | OUTPUTS        |          |     |  |

|--------|----------|----------------|----------|-----|--|

| a      | b        | c<br>(CarryIn) | CarryOut | Sum |  |

| 0      | 0        | 0              | 0        | 0   |  |

| 0      | 0        | 1              | 0        | 1   |  |

| 0      | 1        | 0              | 0        | 1   |  |

| 0      | 1        | 1              | 1        | 0   |  |

| 1      | 0        | 0              | 0        | 1   |  |

| 1      | 0        | 1              | 1        | 0   |  |

| 1      | 1        | 0              | 1        | 0   |  |

| 1      | 1        | 1              | 1        | 1   |  |

#### Sum = $\overline{a} \,\overline{b} \,c + \overline{a} \,b \,\overline{c} + a \,\overline{b} \,\overline{c} + abc$ Carry-Out = $\overline{a} \,bc + a \,\overline{b} \,c + ab \,\overline{c} + abc$

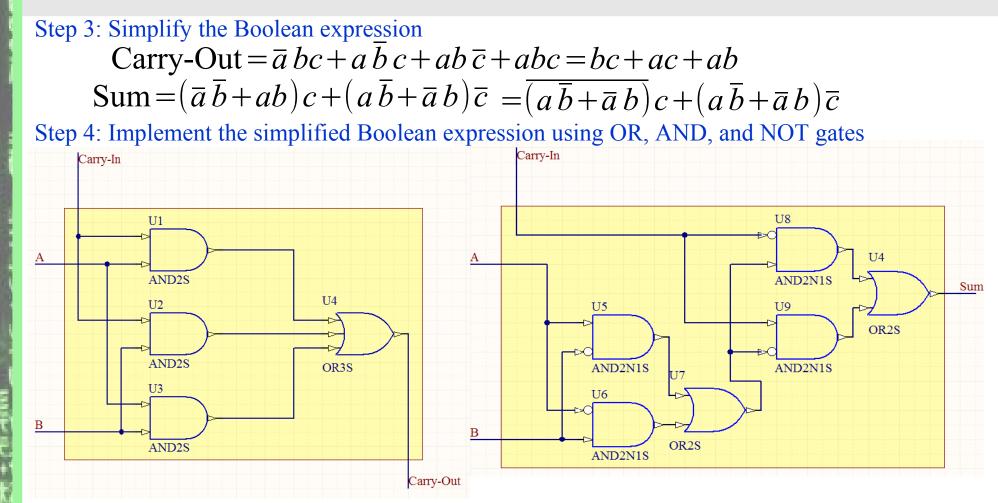

#### Combinational Logic: Design of a 1-bit adder (3)

Activity: Implement the hardware for the Sum output of the 1-bit adder

# Agenda for Today

- Concerns from Prof. Roumani

- 1-bit ALU Logic Design

Patterson: Appendix C

# Prof. Roumani's Concerns

- Not enough students are doing the pre-lab activities at home and as a consequence not very many students are completing the Lab exercises on time

- If you labs have been manually marked, you can pick them up from the TA either at the next lab session or during his office hours (W 16:00 17:00) NO ONE has done this

- All labs have been posted on ePost for Labs A and B. Manually marked Lab C's are to be posted in a few days

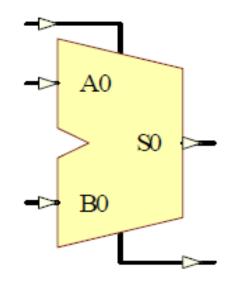

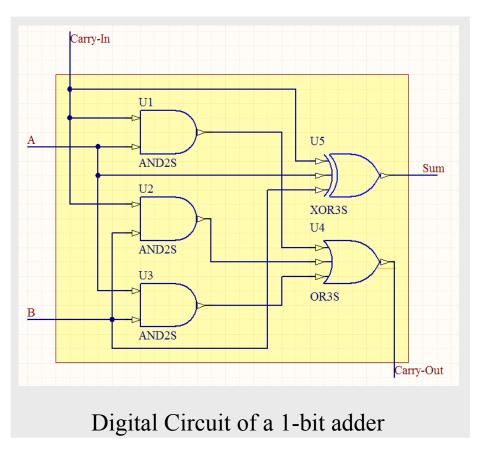

#### 1-bit adder

- Recall the digital circuit of a 1-bit adder

- We will enhance the 1-bit adder to develop a prototype ALU for MIPS

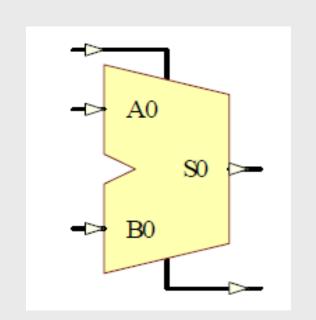

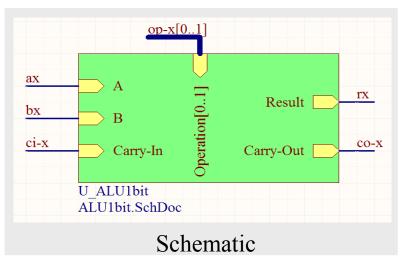

#### Schematic of a 1-bit adder

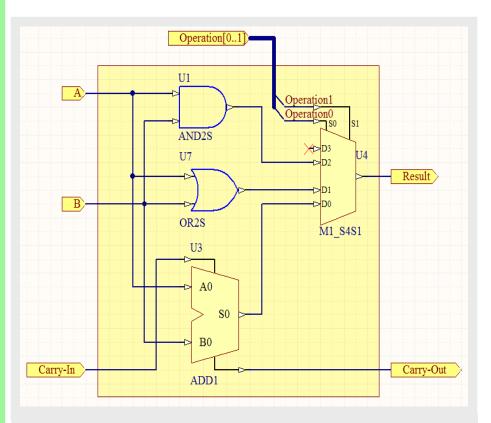

### 1-bit ALU with AND, OR, and Addition

- The 1-bit adder is supplemented with AND and OR gates

- A multiplexer controls which gate is connected to the output

--1

1-bit ALU with AND, OR, and Addition capability

| ALU Contro | Result                  |        |

|------------|-------------------------|--------|

| Carry In   | Operation               | Result |

| 0          | $0=(00)_{\mathrm{two}}$ | add    |

| 0          | $1 = (01)_{two}$        | OR     |

| 0          | $2=(10)_{\rm two}$      | AND    |

-W-5--W

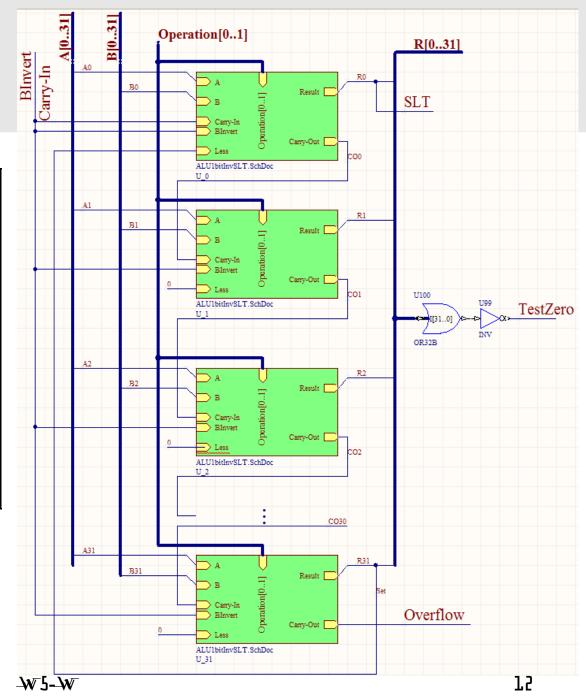

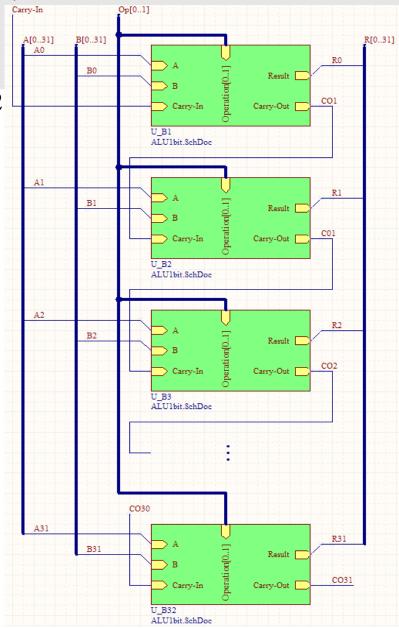

### 32-bit ALU w/ AND, OR, and ADD

- The 1-bit ALU can be cascaded together to form a 32 bit ALU

- Which operation is performed is controlled by the Operation bus

| ALU Contro | Result                  |        |  |

|------------|-------------------------|--------|--|

| Carry In   | Operation               | Kesuit |  |

| 0          | $0=(00)_{\mathrm{two}}$ | add    |  |

| 0          | $1 = (01)_{two}$        | OR     |  |

| 0          | $2=(10)_{\rm two}$      | AND    |  |

• The designed 32-bit ALU is still missing the subtraction, slt (set if less than), and conditional branch operations

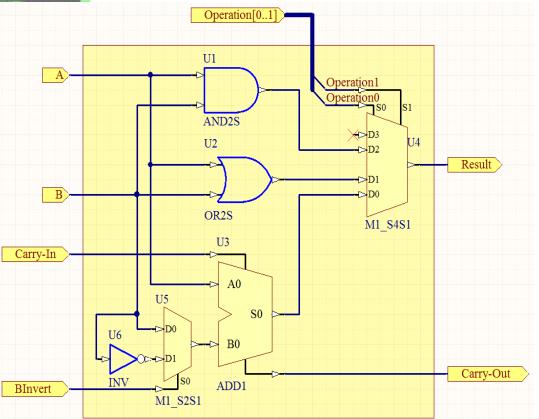

# 1-bit ALU with AND, OR, Addition, and Subtraction

- Recall that subtraction is performed using 2's complement arithmetic

- We calculate the 2's compliment of the sub-operand and add to the first operand

| ALU Contr | Dogult   |                         |     |

|-----------|----------|-------------------------|-----|

| Binvert   | Carry In | Result                  |     |

| 0         | 0        | $2=(10)_{\rm two}$      | AND |

| 0         | 0        | $1 = (01)_{two}$        | OR  |

| 0         | 0        | $0=(00)_{\mathrm{two}}$ | add |

| 1         | 1        | $0=(00)_{\mathrm{two}}$ | sub |

1-bit ALU with AND, OR, Addition, and Subtraction capability

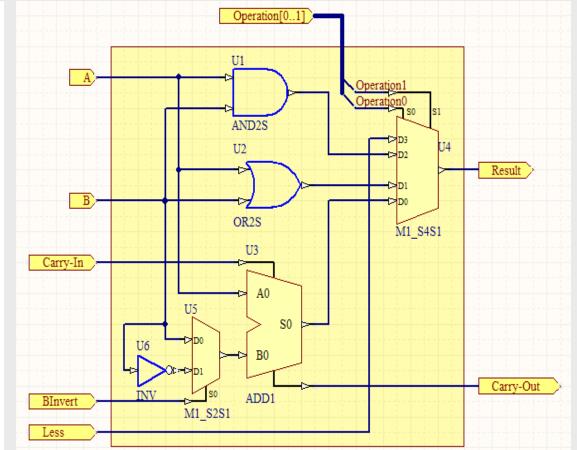

### 1-bit ALU with AND, OR, Add, Sub, and SLT (1)

- Since we need to perform one more operation, we increase the number of inputs at the multiplexer by 1 and label the new input as Less

- SLT operation:

if (a < b), set Less to 1 => if (a − b) < 0, set Less to 1

- SLT operation can therefore be expressed in terms of a subtraction between the two operands.

- If the result of subtraction is negative, set Less to 1.

- How do we determine if the result is negative?

1-bit ALU with AND, OR, Add, Sub, and SLT capability

- To test equality between a and b, subtract b from a and check if the result is 0.  $w_5-w$

U 31

I Ċ ٦,

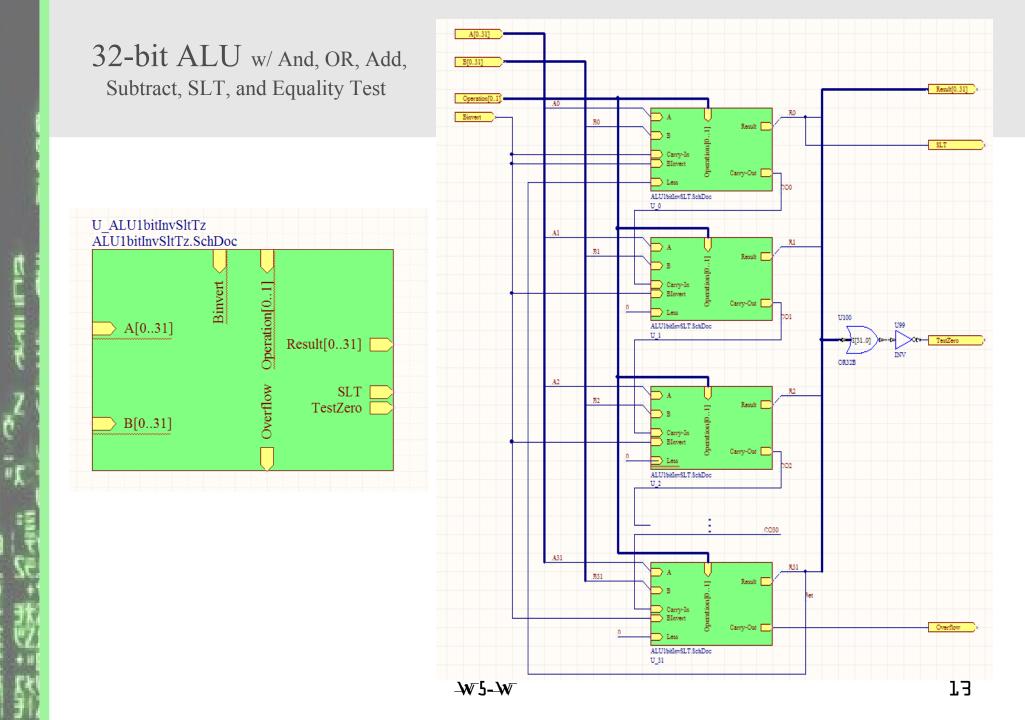

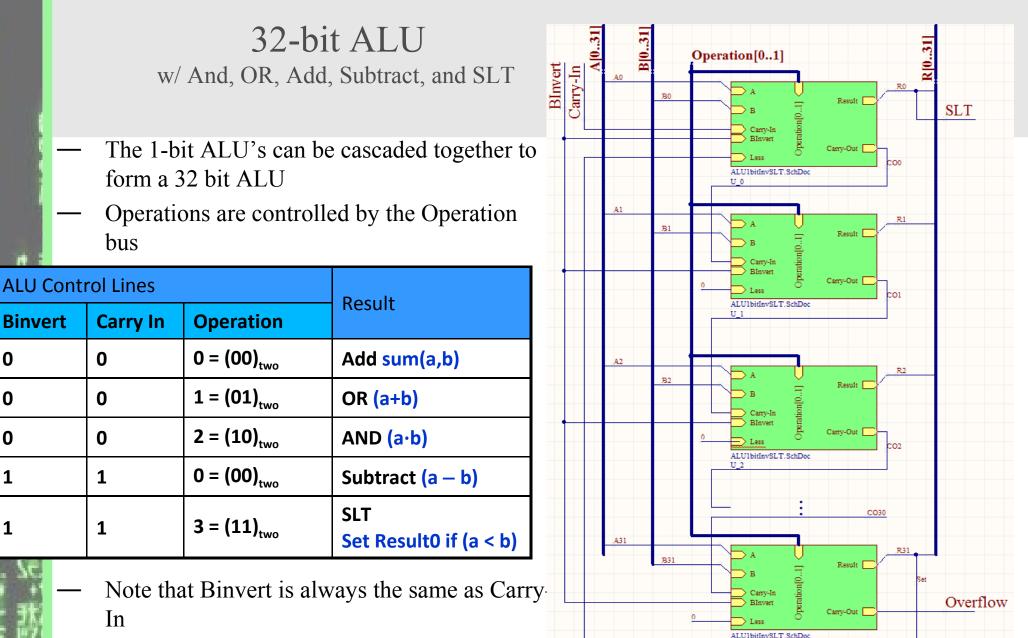

**32-bit ALU** w/ And, OR, Add, Subtract, SLT, and Equality Test

| ALU Co  | ontrol Line | Result             |                                        |  |

|---------|-------------|--------------------|----------------------------------------|--|

| Binvert | Carry In    | Operation          | Kesun                                  |  |

| 0       | 0           | $0=(00)_{\rm two}$ | Add sum(a,b)                           |  |

| 0       | 0           | $1 = (01)_{two}$   | OR (a+b)                               |  |

| 0       | 0           | $2 = (10)_{two}$   | AND (a·b)                              |  |

| 1       | 1           | $0=(00)_{\rm two}$ | Subtract (a - b)                       |  |

| 1       | 1           | $3 = (11)_{two}$   | SLT<br>if (a < b)<br>Result0 = 1       |  |

| 1       | 1           | $0 = (00)_{two}$   | Test Equality<br>Zero = 1 if $(a = b)$ |  |