### -C-S-E==2021== -C-O-M-FU-T-E-R==-O-R-G-A-N-I-Z-A-T-I-O-N

| ]-       |           |             |              |          |            |          |             |          |            | <u>-</u> R- |      | E<br>N<br>T<br>R<br>I<br>T<br>R<br>I<br>I | もレ保の文頼な   | 四十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二 | ンは第一次言方 | REASWOR |    | の文精なフト社      | 一次京江市町 | 11 2 11 2 11 12 11 | 一保の文績なフト     |

|----------|-----------|-------------|--------------|----------|------------|----------|-------------|----------|------------|-------------|------|-------------------------------------------|-----------|-----------------------------------------|---------|---------|----|--------------|--------|--------------------|--------------|

| THOF THE | Z ULNOKUX |             | - 対照 ゆじ笑し 許田 | く 啓勃するふう | 8 m ~ 10.0 | IS YHE M | 甲 び技す 国出のシ品 | *=5 8 08 | の一文精なフィト社明 |             |      |                                           | ト社明 をに美と学 | E                                       | 0 0 1 K |         | 7E | 明 をに美と 字印 び技 |        | COK ZHII           | 杜平 をに美と 字印 び |

| N H E N  | E O A N   | 표 에 03 im 포 | じなす 国出       | 보호 유 2   | 22.67 00   | A<br>T   | 31、毕奋初      | - K P    | をに美と 字印    | 4P          | 王皇王王 |                                           |           |                                         |         | G       | _w | ∑5-]\        | 个      | M.                 | 技士           |

DR

#### **Floating Point Instructions**

| Category      | Instruction                                   | Example              | Meaning                                 | Comments                |

|---------------|-----------------------------------------------|----------------------|-----------------------------------------|-------------------------|

|               | FP add single                                 | add.s \$f2,\$f4,\$f6 | \$f2 ← \$f4+\$f6                        | Single Prec.            |

|               | FP subtract single                            | sub.s \$f2,\$f4,\$f6 | \$f2 ← \$f4-\$f6                        | Single Prec.            |

|               | FP multiply single                            | mul.s \$f2,\$f4,\$f6 | \$f2 ← \$f4×\$f6                        | Single Prec.            |

| Arithmetic    | FP divide single                              | div.s \$f2,\$f4,\$f6 | \$f2 ← \$f4/\$f6                        | Single Prec.            |

| Artunnetic    | FP add double                                 | add.d \$f2,\$f4,\$f6 | \$f2 ← \$f4+\$f6                        | <b>Double Prec.</b>     |

|               | FP subtract double                            | sub.d \$f2,\$f4,\$f6 | \$f2 ← \$f4-\$f6                        | <b>Double Prec.</b>     |

|               | FP multiply double                            | mul.d \$f2,\$f4,\$f6 | \$f2 ← \$f4×\$f6                        | <b>Double Prec.</b>     |

|               | FP divide double                              | div.d \$f2,\$f4,\$f6 | \$f2 ← \$f4/\$f6                        | <b>Double Prec.</b>     |

| Data Transfer | load word FP Single                           | lwc1 \$f2,100(\$s2)  | \$f2 ← Mem[\$s2+100]                    | Single Prec.            |

| Data Transfer | store word FP Single                          | swc1 \$f2,100(\$s2)  | Mem[\$s2+100] ← \$f2                    | Single Prec.            |

|               | FP compare single<br>(eq, ne, lt, le, gt, ge) | c.lt.s \$f2,\$f4     | if(\$f2<\$f4)cond = 1,<br>else cond = 0 | Single Prec.            |

| Conditional   | FP compare double<br>(eq, ne, lt, le, gt, ge) | c.lt.d \$f2,\$f4     | if(\$f2<\$f4)cond = 1,<br>else cond = 0 | Double Prec.            |

| branch        | Branch on FP true                             | bclt 25              | if cond==1 go to<br>PC+100+4            | Single/<br>Double Prec. |

|               | Branch on FP false                            | bclf 25              | if cond==0 go to<br>PC+100+4            | Single/<br>Double Prec. |

|               |                                               | ₩ <b>5</b> -1\/t     |                                         | 2                       |

# Example

|    | # calcul | ate area of a   | circle           |                |   |                                           |

|----|----------|-----------------|------------------|----------------|---|-------------------------------------------|

|    |          | .data           |                  |                |   |                                           |

|    | Ans:     | .asciiz         | "The area of the | circle is:     | " |                                           |

|    | Ans_add: | .word           | Ans              |                | # | Pointer to String (Ans)                   |

|    | Pi:      | .double         | 3.14159265358979 | 24             |   |                                           |

| F  | Rad:     | .double         | 12.3456789012345 | 67             |   |                                           |

| 5  | Rad_add: | .word           | Rad              |                | # | Pointer to float (Rad)                    |

|    |          | .text           |                  |                |   |                                           |

| E. | main:    | lw \$a0, Ans_a  | add (\$0)        |                | # | load address of Ans into \$a0             |

| 5  |          | addi \$v0, \$0, | , 4              |                | # | Sys Call 4 (Print String)                 |

|    |          | syscall         |                  |                |   |                                           |

| R  | #        |                 |                  |                | # | <pre>load float (Pseudoinstruction)</pre> |

|    |          | la \$s0, Pi     |                  |                | # | load address of Pi into \$s0              |

| 5  |          | ldc1 \$f2, 0(\$ | \$s0)            |                | # | \$f2 = Pi                                 |

|    | #        |                 |                  |                | # | load float (MIPS Instruction)             |

|    |          | lw \$s0, Rad_a  | add (\$0)        |                | # | load address of Rad into \$s0             |

| E  |          | ldc1 \$f4, 0(\$ | \$s0)            |                | # | f4 = Rad                                  |

|    |          | mul.d \$f12, \$ | \$f4, \$f4       |                |   |                                           |

|    |          | mul.d \$f12, \$ | \$f12, \$f2      |                |   |                                           |

| H  |          | addi \$v0, \$0, | , 3              |                | # | Sys Call 3 (Print Double)                 |

| -  |          | syscall         |                  |                |   |                                           |

|    | exit:    | jr \$ra         |                  | ) _ <b>F</b> . |   |                                           |

π,

# Agenda for Today

- 1. Floating Point Round off

- 2. Introduction to Hardware Logic Design

Patterson:Section 3.5, Appendix C.1 – C.4Wednesday:Appendix C.5Reminder:Midterm next Wednesday

# Floating Point Round off

- Floating Point arithmetic operations can lead to overflow (like integer arithmetic) and underflow

- Overflow value is too large to be represented by the precision chosen (single or double)

- Underflow value is too small to be represented by the precision chosen

- This situation leads to an exception program/user is alerted (usually by an error message)

- What happens when the answer takes on a value that is between the floating point values that can be represented?

# Example – Floating Point Addition Add: $9.999_{ten} \times 10^{1}$ and $1.610_{ten} \times 10^{-1}$ (assume 3 digits of precision only) $9.99900 \times 10^{1}$ $0.01610 \times 10^{1}$ $10.01510 \times 10^{1} = 1.00151 \times 10^{1} = 1.002 \times 10^{1}$

*IEEE 754 specifies three extra digits for representation of FP calculations* – "guard" and "round" – 2 bits used for multiplication operation

• > 50 - round up, <50 round down, =50?

Rounding modes: always round up, always round down, truncate, round to nearest even

*Third bit* – "*sticky*" – *set when there are digits to the right of the round bit*

# Hardware – Logic Design

- Appendix C goes through the basics of logic devices and how they implement the instructions we have been talking about

- Reference is made to the "Verilog" hardware description language (HDL)

- HDL allows the "designer" (not programmer) to configure all of the programmable logic gates in a FPGA, ASIC or similar device

- HDL is "synthesized" (not compiled) to give a "netlist" (not machine code) which is downloaded to the device

- As the name suggests, HDL describes how the resulting logic circuits will manipulate "signals" (not variables)

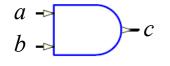

1. AND Gate:

Symbol

$c = a \cdot b = ab$

Notation

Truth Table

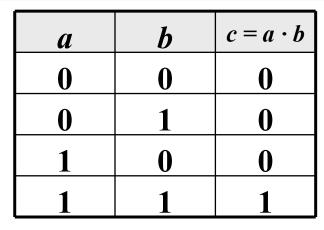

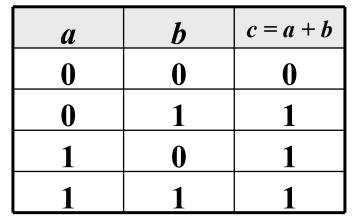

2. OR Gate

۳**۲**

Symbol

c = a + b

Notation

Truth Table

#### Logical Operations: AND, OR, NOT, Multiplexer

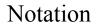

3. NOT Gate (Inverter):

a ->>

Truth Table

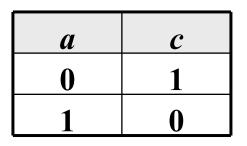

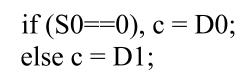

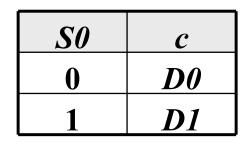

#### 4. Multiplexer

Truth Table

₩**5-**M

Notation

### Boolean Algebra (1)

1. Logic Operations can be expressed in terms of logic equations

- 2. For the above figure, the output  $C = AB + A\overline{B}$

- 3. To implement the above digital circuit, 2 AND, 1 NOT and 1 OR gates are required

- 4. Can we simplify the above circuit?

• [

### Boolean Algebra (1)

|    |                  | Expressions                                            |

|----|------------------|--------------------------------------------------------|

|    | Idontity I aw    | A + <b>0</b> = A                                       |

|    | Identity Law     | $A \cdot 1 = A$                                        |

|    | 7                | A + 1 = 1                                              |

|    | Zero and One Law | $A \cdot 0 = 0$                                        |

|    | Inverse Law      | $A + \bar{A} = 1$                                      |

|    | Inverse Law      | $\bar{A} \cdot 0 = 0$                                  |

| Z  |                  | A + B = B + A                                          |

|    | Commutative law  | $A \cdot B = B \cdot A$                                |

|    | A • 4• <b>T</b>  | A + (B + C) = (A + B) + C                              |

| :5 | Associative Law  | $A \cdot (B \cdot C) = (A \cdot B) \cdot C$            |

| Ē. | Distributive Law | $A \cdot (B + C) = (A \cdot B) + (A \cdot C)$          |

| 20 | Distributive Law | $A + (B \cdot C) = (A + B) \cdot (A + C)$              |

| ţ, | DeMenson Law     | $\overline{(A+B)} = \overline{A} \cdot \overline{B}$   |

|    | DeMorgan Law     | $\overline{(A \cdot B)} = \overline{A} + \overline{B}$ |

|    |                  | ∖₩⊏┖_ौ∧┮                                               |

Simplification Rules

$$A \cdot B + A \cdot \overline{B} = A$$

$A + \overline{A} \cdot B = A + B$

$A + A \cdot B = A$

### Boolean Algebra (2)

Activity 1: Simplify the expressions:

$(a) \quad \overline{AB} + ABC + AB\overline{C}$   $(b) \quad \overline{xyz} + xz$   $(c) \quad (\overline{x} + \overline{y})(\overline{x + y})$   $(d) \quad xy + x(wz + w\overline{z})$  $(e) \quad (B\overline{C} + \overline{AD})(A\overline{B} + C\overline{D})$

Activity 2:

٣ŗ

Implement simplified expressions for (a) - (e) using OR, AND, and NOT gates

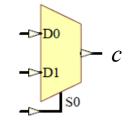

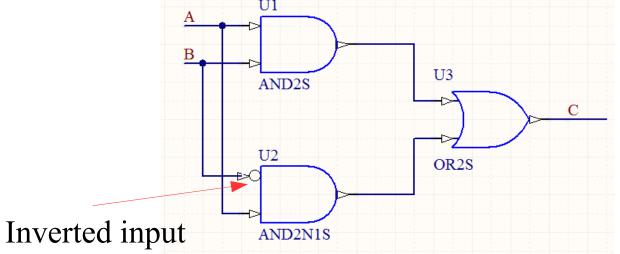

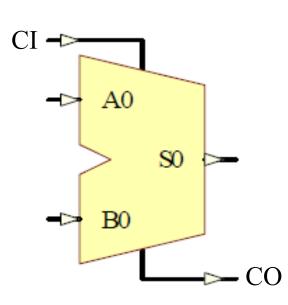

### Combinational Logic: Design of a 1-bit adder (1)

Example: Design a 1-bit adder with Carry-in Step 1: Construct the truth table for a 1-bit adder 3 binary inputs imply  $(2^3 = 8)$  entries in the truth table

|    | INP                         | PUTS             | OUTPUTS           |          |  |  |  |  |

|----|-----------------------------|------------------|-------------------|----------|--|--|--|--|

| AO | <b>B0</b>                   | CI<br>(Carry-In) | CO<br>(Carry-Out) | S0 (Sum) |  |  |  |  |

| 0  | 0                           | 0                | 0                 | 0        |  |  |  |  |

| 0  | 0                           | 1                | 0                 | 1        |  |  |  |  |

| 0  | 1                           | 0                | 0                 | 1        |  |  |  |  |

| 0  | 1                           | 1                | 1                 | 0        |  |  |  |  |

| 1  | 0                           | 0                | 0                 | 1        |  |  |  |  |

| 1  | 0                           | 1                | 1                 | 0        |  |  |  |  |

| 1  | 1                           | 0                | 1                 | 0        |  |  |  |  |

| 1  | 1                           | 1                | 1                 | 1        |  |  |  |  |

|    | Truth Table for 1 bit adder |                  |                   |          |  |  |  |  |

Truth Table for 1-bit adder

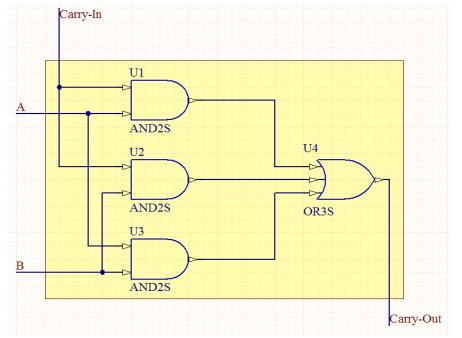

Schematic of a 1-bit adder

Step 2: Derive the Boolean expression for each output from the truth table

|                                                                                                                                                                                   | INPUTS | OUTPUTS         |           |     |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------|-----------|-----|--|--|--|

| a                                                                                                                                                                                 | b      | c<br>(Carry-In) | Carry-Out | Sum |  |  |  |

| 0                                                                                                                                                                                 | 0      | 0               | 0         | 0   |  |  |  |

| 0                                                                                                                                                                                 | 0      | 1               | 0         | 1   |  |  |  |

| 0                                                                                                                                                                                 | 1      | 0               | 0         | 1   |  |  |  |

| 0                                                                                                                                                                                 | 1      | 1               | 1         | 0   |  |  |  |

| 1                                                                                                                                                                                 | 0      | 0               | 0         | 1   |  |  |  |

| 1                                                                                                                                                                                 | 0      | 1               | 1         | 0   |  |  |  |

| 1                                                                                                                                                                                 | 1      | 0               | 1         | 0   |  |  |  |

| 1                                                                                                                                                                                 | 1      | 1               | 1         | 1   |  |  |  |

| Sum = $\overline{a} \overline{b} c + \overline{a} b \overline{c} + a \overline{b} \overline{c} + abc$<br>Carry-Out = $\overline{a} bc + a \overline{b} c + ab \overline{c} + abc$ |        |                 |           |     |  |  |  |

Combinational Logic: Design of a 1-bit adder (3)

Step 3: Simplify the Boolean expression

Carry-Out =

$$\overline{a} bc + a \overline{b} c + ab \overline{c} + abc = bc + ac + ab$$

Step 4: Implement the simplified Boolean expression using OR, AND, and NOT gates

Activity: Implement the hardware for the Sum output of the 1-bit adder