# -C-S-E==2021== -C-O-M-FU-T-E-R==-O-R-G-A-N-I-Z-A-T-I-O-N

| ]-          |               |               |             |             |           |             |             |           |              | Ē        |    |            | N T O U R I | もと保の文制な |   | ンは第一ズ富万                    | REANWOR | au 0.0 ma | の文精なフト社     | 「東京江北町・ | 11 M M T - 1 C | 住の びれなご 1            |

|-------------|---------------|---------------|-------------|-------------|-----------|-------------|-------------|-----------|--------------|----------|----|------------|-------------|---------|---|----------------------------|---------|-----------|-------------|---------|----------------|----------------------|

| THUTTURN    | A M W O R L D | 0220 28       | ト 対明 ゆじ笑と 学 | north, teàt | 10 A 12 4 | H 57 > 포 H  | 中 び技す 国出のシロ | *=** ** * | 10 4 2 4 G 1 | の文精なフト社明 |    |            |             | ト社明をに美と | E | о<br>0<br>0<br>1<br>к<br>1 |         | E         | 明 をに美と 字印 び |         | STUN YOU       | The Automatic States |

| 2 2 H H H H | NEOKZ         | 프 + U H - H H | 印じ技す 国出     | ∧ 2 m A :   | \$ 2147 W | M<br>A<br>T | 311 원출전 원   | 14 H      |              | をに美と 学田  | 4P | TH R H H H |             |         |   |                            | A<br>G  | -₩        | 5\4         | ,<br>₽  | H'             |                      |

DR

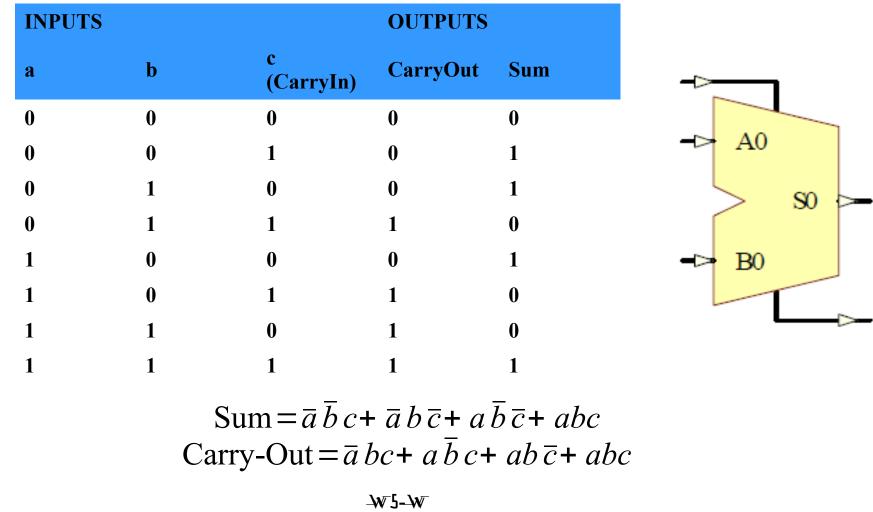

# Combinational Logic: Design of a 1-bit adder (2)

Step 2: Derive the Boolean expression for each output from the truth table

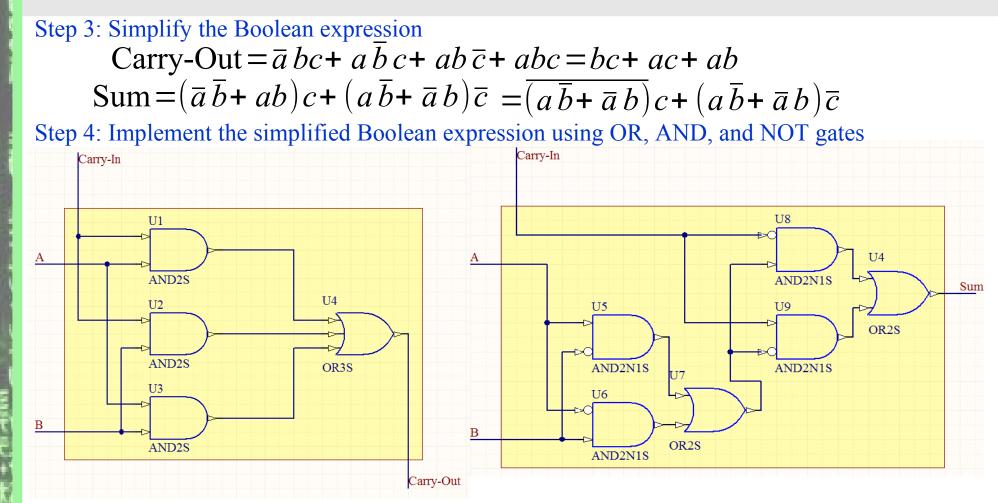

### Combinational Logic: Design of a 1-bit adder (3)

Activity: Implement the hardware for the Sum output of the 1-bit adder

# Agenda for Today

1-bit ALU – Logic Design

Patterson:Appendix C.5No Labs next week, Midterm on Wednesday

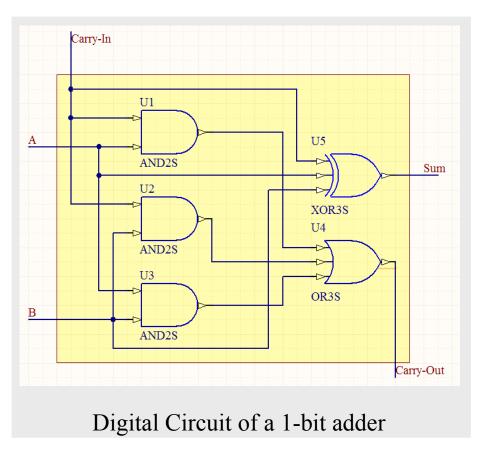

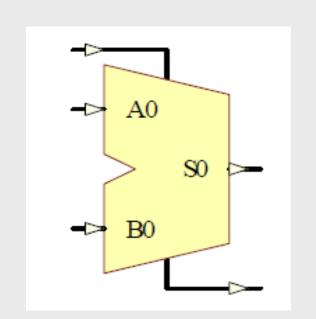

### 1-bit adder

- Recall the digital circuit of a 1-bit adder

- We will enhance the 1-bit adder to develop a prototype ALU for MIPS

#### Schematic of a 1-bit adder

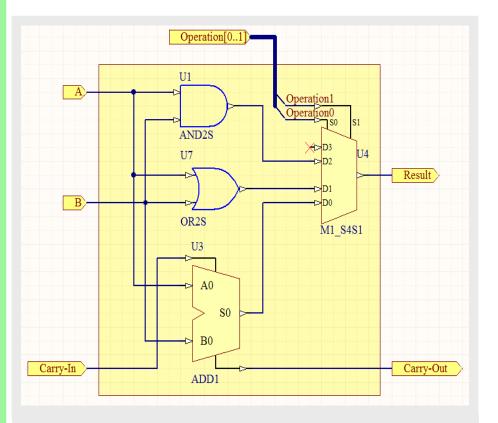

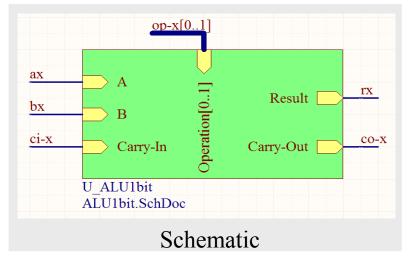

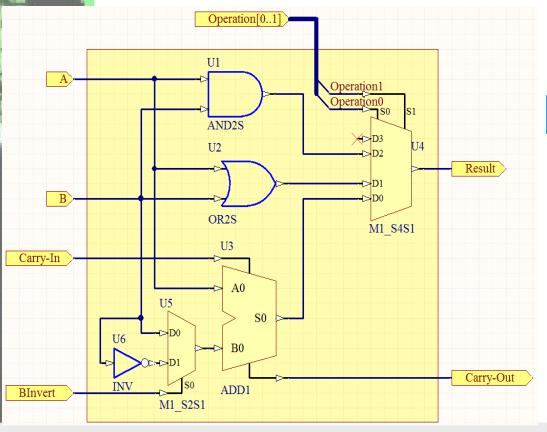

### 1-bit ALU with AND, OR, and Addition

- The 1-bit adder is supplemented with AND and OR gates

- A multiplexer controls which gate is connected to the output

--1

1-bit ALU with AND, OR, and Addition capability

| ALU Contr       | ALU Control Lines       |        |  |  |  |  |

|-----------------|-------------------------|--------|--|--|--|--|

| <b>Carry In</b> | Operation               | Result |  |  |  |  |

| 0               | $0=(00)_{\mathrm{two}}$ | add    |  |  |  |  |

| 0               | $1 = (01)_{two}$        | OR     |  |  |  |  |

| 0               | $2 = (10)_{two}$        | AND    |  |  |  |  |

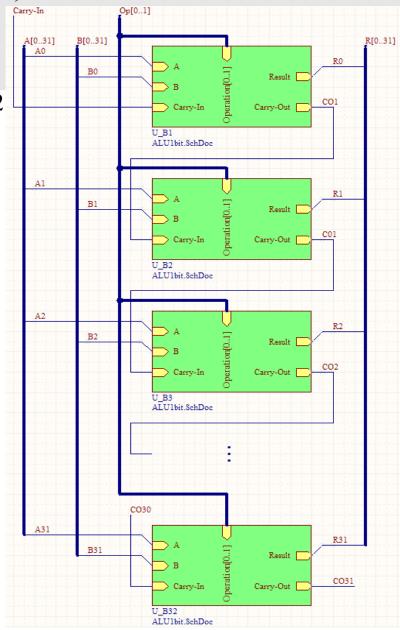

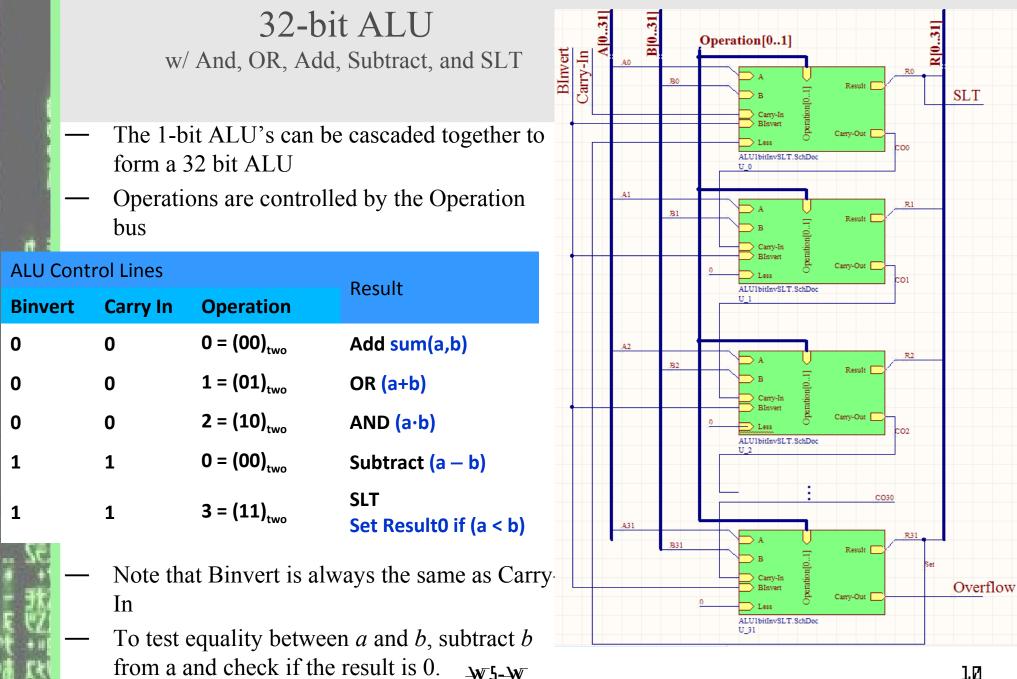

### 32-bit ALU w/ AND, OR, and ADD

- The 1-bit ALU can be cascaded together to form a 32 bit ALU

- Which operation is performed is controlled by the Operation bus

| ALU Contr | Result                  |         |  |  |  |

|-----------|-------------------------|---------|--|--|--|

| Carry In  | Operation               | ixesuit |  |  |  |

| 0         | $0=(00)_{\mathrm{two}}$ | add     |  |  |  |

| 0         | $1 = (01)_{two}$        | OR      |  |  |  |

| 0         | $2 = (10)_{two}$        | AND     |  |  |  |

• The designed 32-bit ALU is still missing the subtraction, slt (set if less than), and conditional branch operations

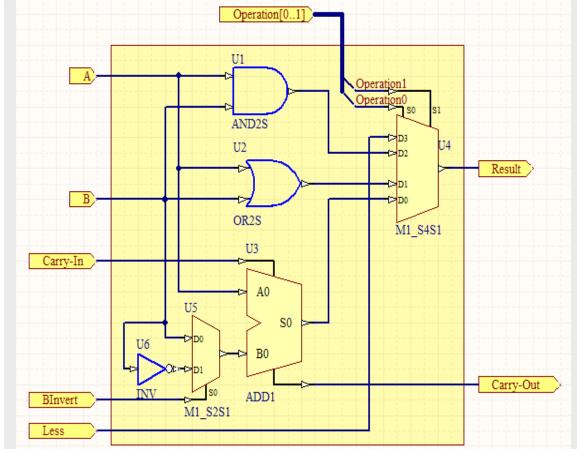

# 1-bit ALU with AND, OR, Addition, and Subtraction

- Recall that subtraction is performed using 2's complement arithmetic

- We calculate the 2's compliment of the sub-operand and add to the first operand

| ALU Control Lines |          |                         |        |  |  |  |  |  |  |

|-------------------|----------|-------------------------|--------|--|--|--|--|--|--|

| Binvert           | Carry In | Operation               | Result |  |  |  |  |  |  |

| 0                 | 0        | $2 = (10)_{two}$        | AND    |  |  |  |  |  |  |

| 0                 | 0        | $1 = (01)_{two}$        | OR     |  |  |  |  |  |  |

| 0                 | 0        | $0=(00)_{\mathrm{two}}$ | add    |  |  |  |  |  |  |

| 1                 | 1        | $0=(00)_{\mathrm{two}}$ | sub    |  |  |  |  |  |  |

1-bit ALU with AND, OR, Addition, and Subtraction capability

### 1-bit ALU with AND, OR, Add, Sub, and SLT (1)

- Since we need to perform one more operation, we increase the number of inputs at the multiplexer by 1 and label the new input as Less

- SLT operation:

if (a < b), set Less to 1 => if (a − b) < 0, set Less to 1

- SLT operation can therefore be expressed in terms of a subtraction between the two operands.

- If the result of subtraction is negative, set Less to 1.

- How do we determine if the result is negative?

1-bit ALU with AND, OR, Add, Sub, and SLT capability

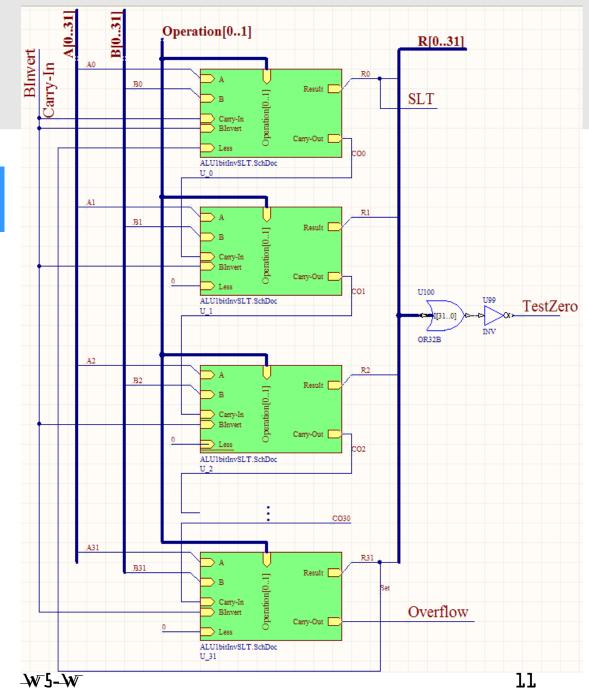

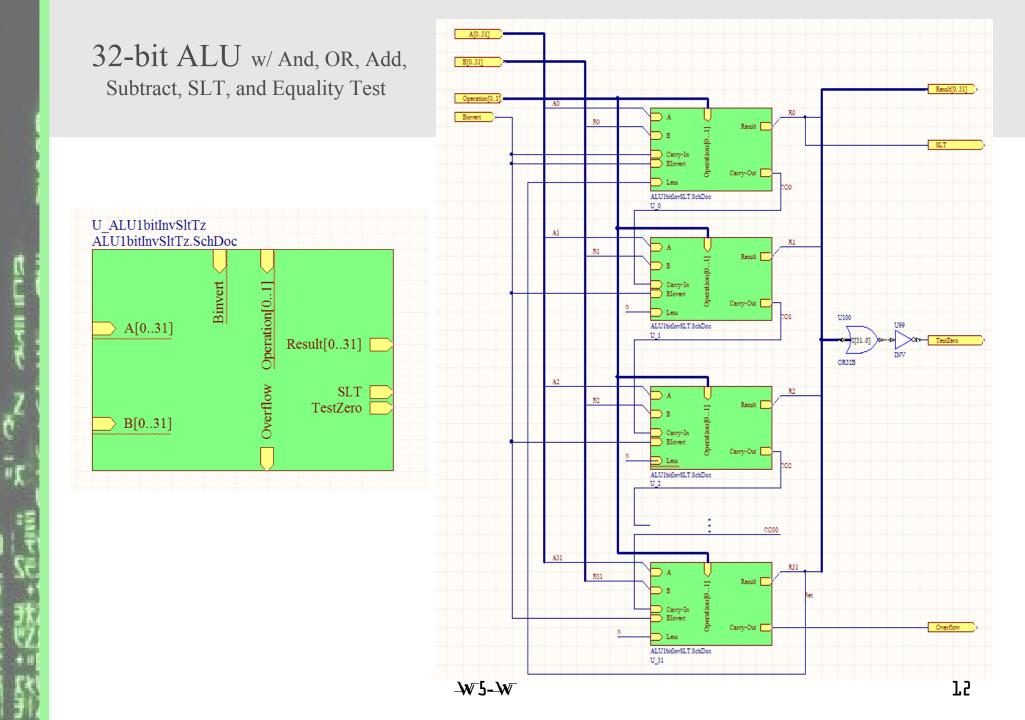

**32-bit ALU** w/ And, OR, Add, Subtract, SLT, and Equality Test

| ALU Co           | ontrol Line | Dequit             |                                        |  |  |  |  |  |

|------------------|-------------|--------------------|----------------------------------------|--|--|--|--|--|

| Binvert Carry In |             | Operation          | Result                                 |  |  |  |  |  |

| 0                | 0           | $0=(00)_{\rm two}$ | Add sum(a,b)                           |  |  |  |  |  |

| 0                | 0           | $1 = (01)_{two}$   | OR (a+b)                               |  |  |  |  |  |

| 0                | 0           | $2 = (10)_{two}$   | AND (a·b)                              |  |  |  |  |  |

| 1                | 1           | $0=(00)_{\rm two}$ | Subtract (a - b)                       |  |  |  |  |  |

| 1                | 1           | $3 = (11)_{two}$   | SLT<br>if (a < b)<br>Result0 = 1       |  |  |  |  |  |

| 1                | 1           | $0 = (00)_{two}$   | Test Equality<br>Zero = 1 if $(a = b)$ |  |  |  |  |  |

|                  |             |                    |                                        |  |  |  |  |  |

|                  |             |                    |                                        |  |  |  |  |  |

Ċ

I

H

I