## -C-SE==2021== -C-O-MFUTE-R==-O-R-GANIZATIO-N

| Ţ        |               |             |              |              |             |           | .[]<br>.[]   |             |                 | <u>]</u>     | R_= |           | Y T<br>U T<br>R | もと保の文精      | 200.000 | シはアメ富万    | REAMWO | m+Orb nu        | の文積なフト         | 一般市江市町     | 19 B 10 B 10 B 10 | 保の文積なフ         |

|----------|---------------|-------------|--------------|--------------|-------------|-----------|--------------|-------------|-----------------|--------------|-----|-----------|-----------------|-------------|---------|-----------|--------|-----------------|----------------|------------|-------------------|----------------|

| THOTINGU | A NO NO NO NO | ++ ac as co | - 社部 ゆじ笑と 学日 | ✓ 10181-1 10 | 8 00 A 20 8 | HS YHE MA | 中び技す 国出のシ品 数 | 8 IN 10 08- | E O A N A G E N | の一文精なフィト社明。を |     |           |                 | なフト社開をに美と学印 | E       | 8 08-× 40 |        | E international | 社明 をに美と 字印 び技す | ZON WENTER |                   | 「台湾」をに美と 字印 びま |

| 2112     | 0<br>A<br>N   | 프 너 10 년 프  | び技す 国出       | 보여 유 :       | 22.147 00   | T T       | 311、 9- @ 5  | - 2 2.      |                 | に美と 字印       | Ť   | m ∓ + m + | 1 0             |             |         | j         | G      | -₩F             | an<br>}-₩      | -          | 1                 | 27             |

DR

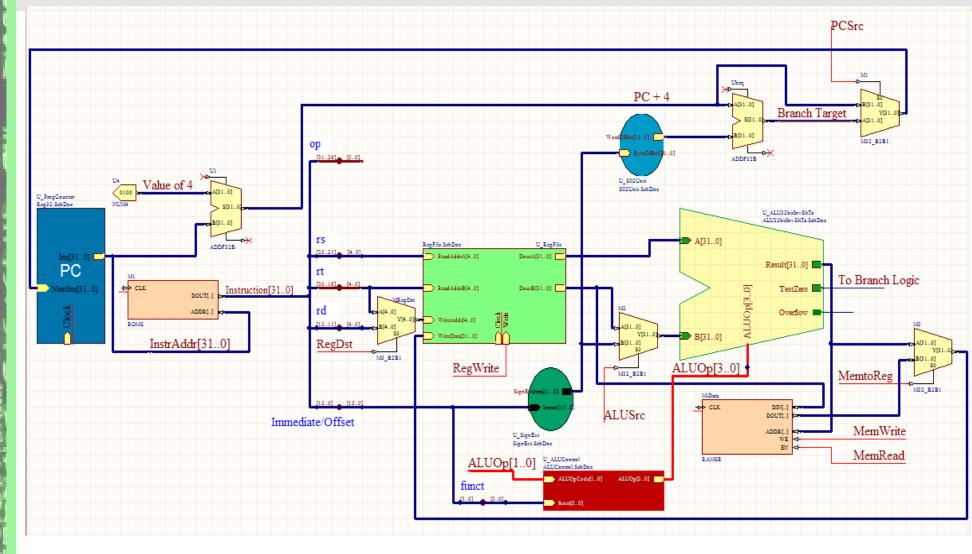

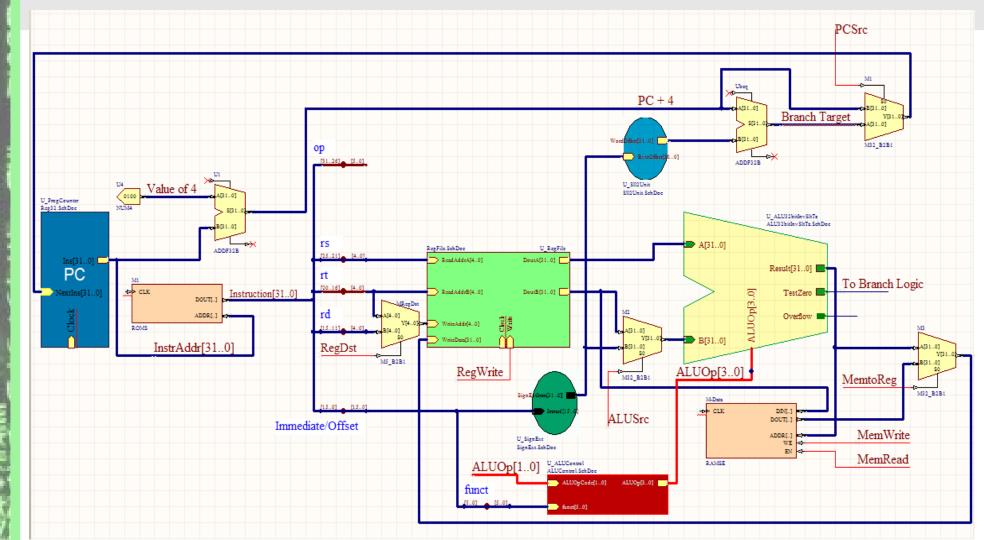

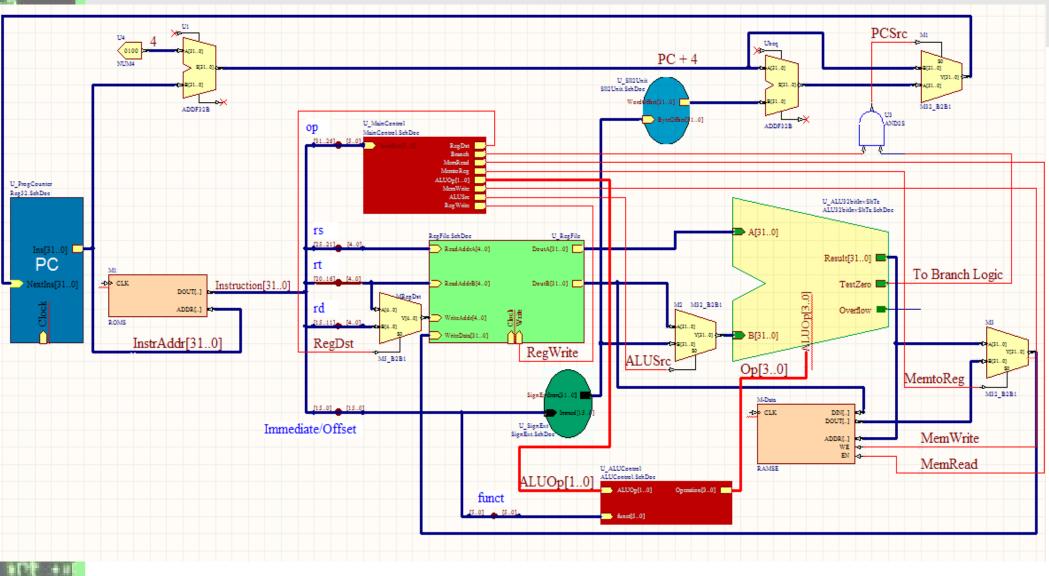

## **Combined Datapath**

न्त्रं.

۰

ć

ī,

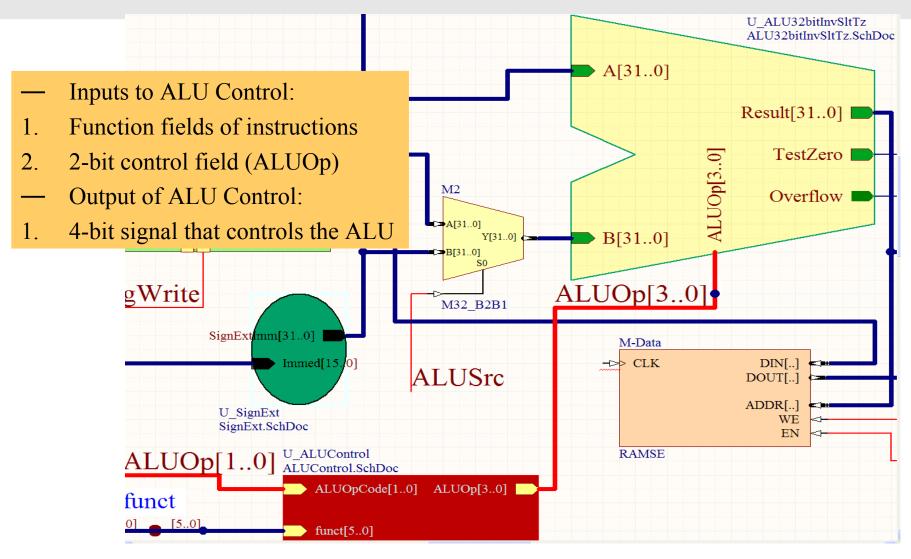

## Control: ALU Control Unit (1)

۳٢

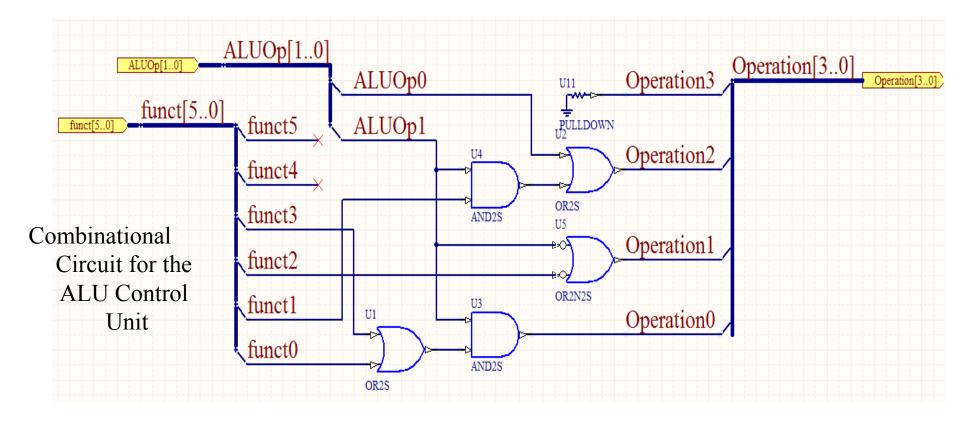

## Control: ALU Control Unit (4)

|                        | Inputs                        |   |     |    |                             |   |   |   |   |                       |                                     |      |  |

|------------------------|-------------------------------|---|-----|----|-----------------------------|---|---|---|---|-----------------------|-------------------------------------|------|--|

| Instruction<br>(funct) | ALUOp<br>(ALUOp1 –<br>ALUOp0) |   |     | F  | Function Field<br>(F5 – F0) |   |   |   | d | Desired ALU<br>action | Outputs<br>Operation<br>(Op3 – Op0) |      |  |

| lw (I)                 | 0                             | Х | ( ) | 0) | Х                           | Х | Х | Х | Х | Х                     | add                                 | 0010 |  |

| sw (I)                 | 0                             | Х | ( ) | 0) | Х                           | Х | Х | Х | Х | Х                     | add                                 | 0010 |  |

| beq (I)                | Х                             | 1 | ( ) | 1) | Х                           | Х | Х | Х | Х | Х                     | sub                                 | 0110 |  |

| add (32)               | 1                             | Х | (1  | 0) | Х                           | Х | 0 | 0 | 0 | 0                     | add                                 | 0010 |  |

| sub (34)               | 1                             | Х | (1  | 0) | Х                           | Х | 0 | 0 | 1 | 0                     | sub                                 | 0110 |  |

| and (36)               | 1                             | Х | (1  | 0) | Х                           | Х | 0 | 1 | 0 | 0                     | and                                 | 0000 |  |

| or (37)                | 1                             | Х | (1  | 0) | Х                           | Х | 0 | 1 | 0 | 1                     | or                                  | 0001 |  |

| slt (42)               | 1                             | Х | (1  | 0) | Х                           | Х | 1 | 0 | 1 | 0                     | slt                                 | 0111 |  |

Simplified Expressions:

$Op0 = ALUOp1 \cdot (F0 + F3)$   $Op1 = \overline{ALUOp1} + \overline{F2}$  $Op2 = ALUOp0 + ALUOp1 \cdot F1$

# Agenda

## Topics:

- 1. A single cycle implementation (complete this)

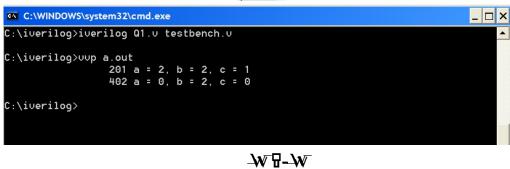

- 2. iverilog Example

- 3. Lab D double precision version

Patterson: Section 4.3, 4.4

Reminder: No class next Wednesday, Quiz 2 is following Wednesday, Lab K (Verilog) next week

## Control: ALU Control Unit (5)

$Op0 = ALUOp1 \cdot (F0 + F3)$   $Op1 = \overline{ALUOp1} + \overline{F2} = \overline{ALUOp1 \cdot F2}$  $Op2 = ALUOp0 + ALUOp1 \cdot F1$

٦.

6

## Main Control (1)

| R-format: | op (31 – 26) | rs (25 – 21) | rt (20 – 16) | rd (15 – 11) | shamt (10 – 6)   | funct (5 – 0) |

|-----------|--------------|--------------|--------------|--------------|------------------|---------------|

| I-format: | op (31 – 26) | rs (25 – 21) | rt (20 – 16) | Immed        | liate / Offset ( | (15 – 0)      |

- 1. Opcode is contained in bits 31 26.

- 2. Registers specified by rs (bits 25 21) and rt (bits 20 16) are always read

- 3. Base register (w/ base address) for lw/sw instruction is specified by rs (bits 25–21)

- 4. 16-bit offset for **beq**, lw, and sw is always specified in bits 15 0.

- 5. Destination register is specified in one of the two places:

- For R-type instructions (add/sub/and/or), destination register is specified by bits (15 11)

- For lw instruction, destination register is specified by bits (20 16)

Using information (1 - 5), we can add the instruction labels and additional MUX's to the datapath that we have constructed.

## Main Control (2)

Ċ

. ٦"

Number of control lines is 11 (4 for MUX's, 4 for ALU control, 2 for data memory, 1 for register file)

## Main Control (3)

| <b>Control Input</b> | Effect when Deasserted (0)                                                                               | Effect when asserted (1)                                                                                                                        |

|----------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| RegDst               | Destination register number comes from bits $20 - 16$ of the instruction (sw)                            | Destination register number comes from bits 15 – 11 of the instruction (add, sub, or, and, slt)                                                 |

| Regwrite             | None                                                                                                     | Data on the "write data" input is written on the register specified on the "write register" input (lw, add, sub, or, and)                       |

| ALUSrc               | Second operand to ALU comes from the second register file output (add, sub, or, and, beq, slt)           | Second operand to ALU is sign extended, lower 16 bits of instruction(lw,sw)                                                                     |

| MemRead              | None                                                                                                     | Data from memory location specified by "address" input is placed on the "read data" output (lw)                                                 |

| MemWrite             | None                                                                                                     | Data from "write data" input replaces memory location specified by "address" input (sw)                                                         |

| MemtoReg             | Data from the output of ALU is fed into "write data" input of the register file (add, sub, or, and, slt) | Data from the "read data" output of data memory is fed into "write data" input of the register file $(lw)$                                      |

| PCSrc                | PC is replaced by the output of adder which adds 4 to the existing content of PC (except for beq)        | PC is replaced by the output of adder which computes<br>branch target by adding existing content of PC with<br>2-bit right shifted offset (beq) |

|                      |                                                                                                          |                                                                                                                                                 |

Next step in the design of datapath is to add a control unit that generates the control inputs to MUX's

## Main Control (4)

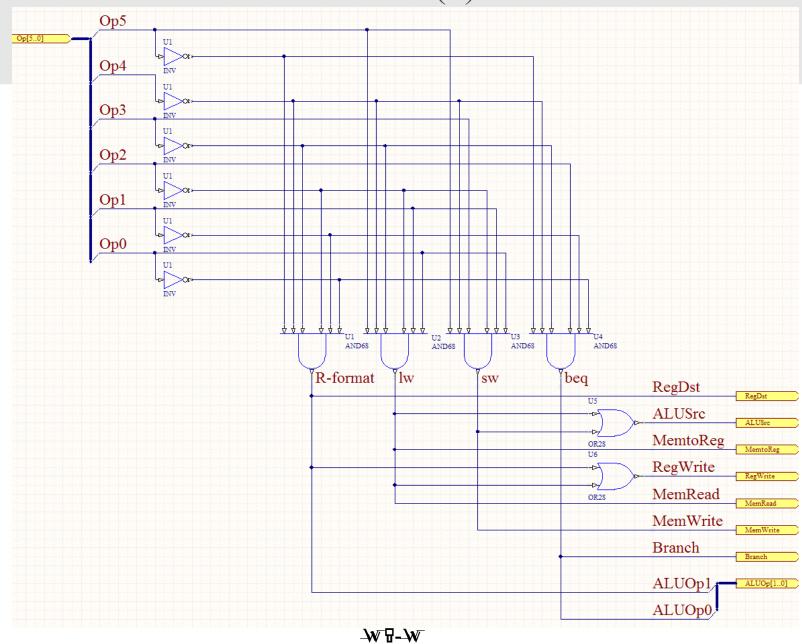

## Main Control (5)

Control Unit Inputs:

| Instruction | Opcode in                | Opcode in Binary |     |     |     |     |     |  |  |  |  |

|-------------|--------------------------|------------------|-----|-----|-----|-----|-----|--|--|--|--|

|             | Decimal                  | Op5              | Op4 | Op3 | Op2 | Op1 | Op0 |  |  |  |  |

| R-format    | 0 <sub>ten</sub>         | 0                | 0   | 0   | 0   | 0   | 0   |  |  |  |  |

| lw          | 35 <sub>ten</sub>        | 1                | 0   | 0   | 0   | 1   | 1   |  |  |  |  |

| SW          | <b>43</b> <sub>ten</sub> | 1                | 0   | 1   | 0   | 1   | 1   |  |  |  |  |

| beq         | 4 <sub>ten</sub>         | 0                | 0   | 0   | 1   | 0   | 0   |  |  |  |  |

### Outputs of Control Unit:

| Instruction     | RegDst | ALUSrc  | MemtoReg | RegWrite | MemRead | MemWrite | Branch | ALUOp1 | ALUOp0 |

|-----------------|--------|---------|----------|----------|---------|----------|--------|--------|--------|

| <b>R-format</b> | 1      | 0       | 0        | 1        | 0       | 0        | 0      | 1      | 0      |

| lw              | 0      | 1       | 1        | 1        | 1       | 0        | 0      | 0      | 0      |

| SW              | X      | 1       | X        | 0        | 0       | 1        | 0      | 0      | 0      |

| beq             | X      | 0       | X        | 0        | 0       | 0        | 1      | 0      | 1      |

|                 | 1      | 0 . 1 1 | . •      |          |         |          |        |        |        |

...above 2 tables constitute the truth table ₩₽-₩

### Main Control (6)

Ċ

זי

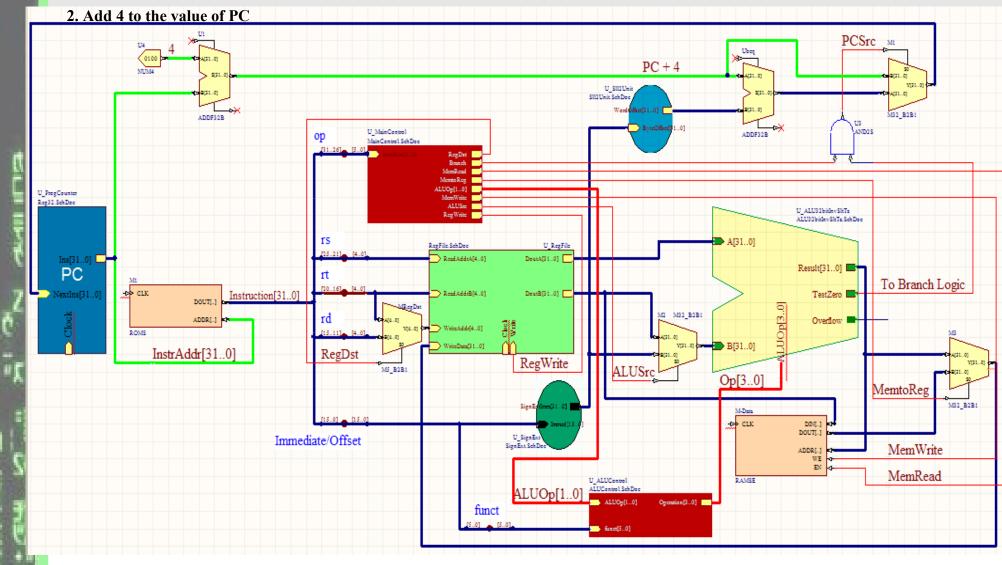

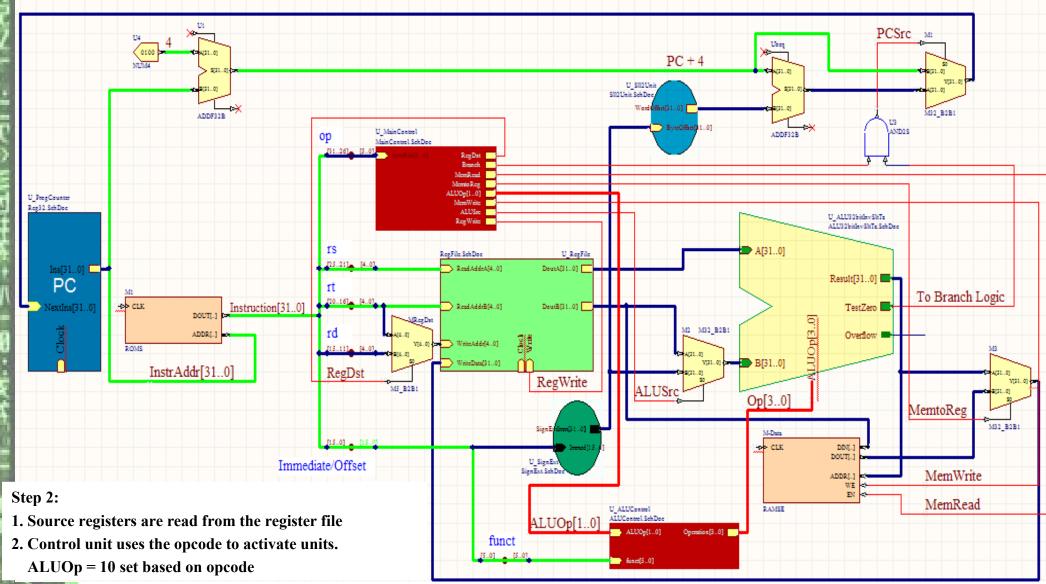

### Example: R-type Instruction (step1: fetch instruction & increment PC)

Step 1

IC I

11

B

1. Fetch instruction

### Example: R-type Instruction (step2: Read two source registers)

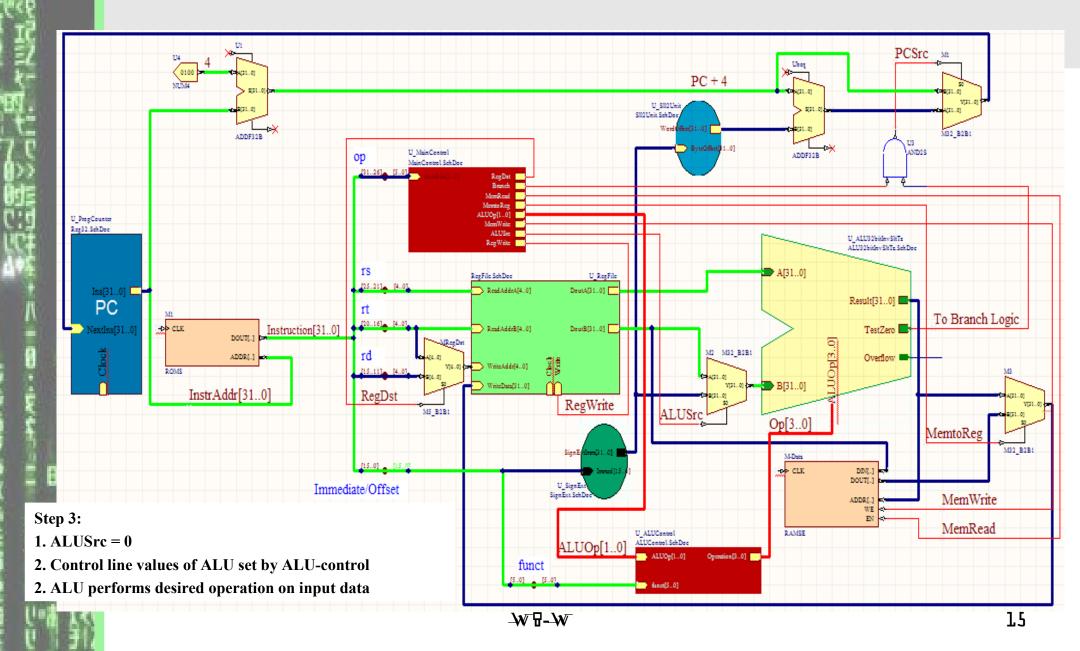

### Example: R-type Instruction (step3: ALU operates on operands)

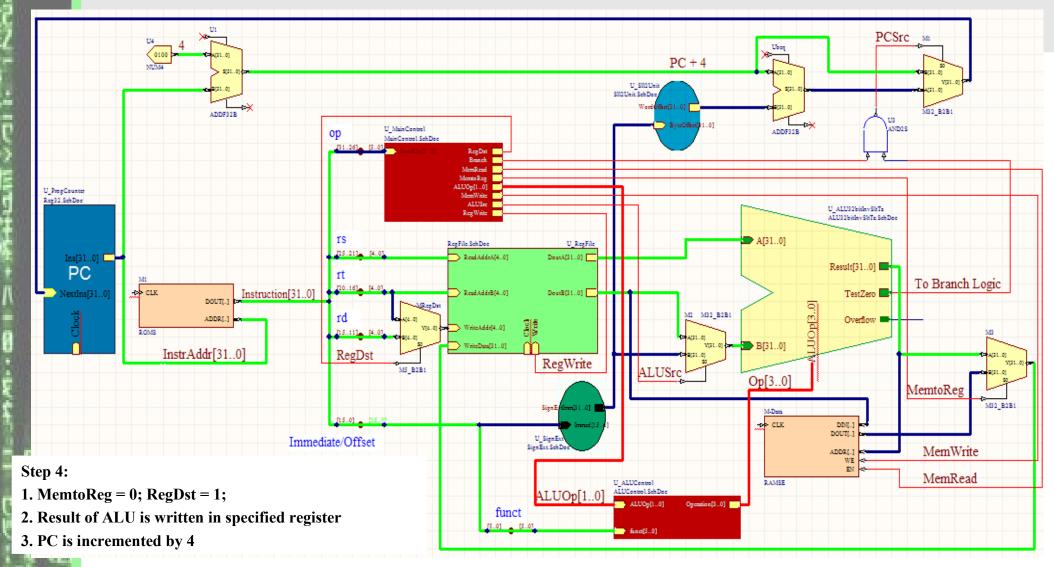

### Example: R-type Instruction (step 4: Write result in destination register)

## Why is single-cycle implementation not used?

Assuming no delay at adder, sign extension unit, shift left unit, PC, control unit, and MUX:

- Load cycle requires 5 functional units:

- instruction fetch, register access, ALU, data memory access, register access

- Store cycle requires 4 functional units:

- instruction fetch, register access, ALU, data memory access

- R-type instruction cycle requires 4 functional units:

instruction fetch, register access, ALU, register access

- Path for a branch instruction requires 3 functional units: instruction fetch, register access, ALU

- Path for a jump instruction requires 1 functional unit: instruction fetch

Using a clock cycle of equal duration for each instruction is a waste of resources.

## iverilog Example

| C:\iverilog\Q1.v - Notepad++                                                 | C:\iverilog\testbench.v - Notepad++                                                |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| File Edit Search View Encoding Language Settings Macro Run TextFX Plugins Wi |                                                                                    |

|                                                                              |                                                                                    |

| Q1.v testbench.v                                                             | alv Estbench.v                                                                     |

| 1 module eq2_sop                                                             | 1 module testbench;                                                                |

| 2 📮 🌔                                                                        | <pre>2 reg [1:0] test_a, test_b;</pre>                                             |

| 3 input wire[1:0] a, b,                                                      | 3 wire test_c;                                                                     |

| 4 output wire aeqb                                                           | 4                                                                                  |

| 5 <sup>L</sup> );                                                            | <pre>5 eq2_sop uut_eq2(test_a, test_b, test_c);</pre>                              |

| 6                                                                            | 6                                                                                  |

| 7 // internal signal declaration                                             | 7 initial                                                                          |

| 8 wire p0, p1, p2, p3;                                                       | 8 = begin                                                                          |

| 9                                                                            | 9 #200                                                                             |

| 10 //sum of product terms                                                    | 10 test_a = 2'b10;                                                                 |

| 11 <b>assign</b> aeqb = p0   p1   p2   p3;                                   | 11 test_b = 2'b10;                                                                 |

| 12 // product terms                                                          | 12 <b>#1</b> \$display(\$time, " a = %d, b = %d, c = %d",test_a, test_b, test_c);  |

| 13 assign p0 = (~a[1] & ~b[1]) & (~a[0] & ~b[0]);                            | 13 <b>#</b> 200                                                                    |

| 14 assign p1 = (~a[1] & ~b[1]) & (a[0] & b[0]);                              | 14 test_a = 2'b00;                                                                 |

| 15 assign p2 = (a[1] & b[1]) & (~a[0] & ~b[0]);                              | 15 test_b = 2'b10;                                                                 |

| 16 assign p3 = (a[1] & b[1]) & (a[0] & b[0]);                                | 16 <b>#</b> 1 \$display(\$time, " a = %d, b = %d, c = %d",test_a, test_b, test_c); |

| 17                                                                           | 17 end                                                                             |

| 18 endmodule                                                                 | 18 endmodule                                                                       |

## Lab D – Double Precision Read/Write

# CSE2021 Lab D

# Name: removed

# csexxxxx s/n yyy yyy yyy

# October nn, 2012

# TABS ARE SET TO 4

|     |          | .data                                                                       |          |                  |                                    |  |  |  |  |  |

|-----|----------|-----------------------------------------------------------------------------|----------|------------------|------------------------------------|--|--|--|--|--|

| P   | HEAD:    | .word                                                                       | 0        |                  | <pre># pointer to first node</pre> |  |  |  |  |  |

| ŝ.  | message: | .asciiz                                                                     | "Enter   | a double precis  | ion number (-1 to stop): \n"       |  |  |  |  |  |

| 54  |          | .text                                                                       |          |                  |                                    |  |  |  |  |  |

| 15  |          | **********                                                                  |          |                  |                                    |  |  |  |  |  |

| 61  |          | # main procedure                                                            |          |                  |                                    |  |  |  |  |  |

| ς,  |          | #                                                                           |          |                  |                                    |  |  |  |  |  |

|     |          | <pre># 12-10-23: modified to read double precision values - H.Chesser</pre> |          |                  |                                    |  |  |  |  |  |

| X   |          | <pre># 12-10-23: modified to prompt user for values</pre>                   |          |                  |                                    |  |  |  |  |  |

|     |          | *****                                                                       |          |                  |                                    |  |  |  |  |  |

|     | main:    | SW                                                                          | Şra,     | 0(\$sp)          |                                    |  |  |  |  |  |

| Ш   |          | addi                                                                        | Şsp,     | \$sp, -4         | #opening main                      |  |  |  |  |  |

|     |          | # Read &                                                                    | proces   | s loop           |                                    |  |  |  |  |  |

|     |          | # Read :                                                                    | int valu | es from user one | at a time and process them         |  |  |  |  |  |

| E.  |          | # Ends (                                                                    | on input | -1.0e0           |                                    |  |  |  |  |  |

|     | prompt:  | li                                                                          | \$v0,    | 4                |                                    |  |  |  |  |  |

|     |          | la                                                                          | \$a0,    | message          |                                    |  |  |  |  |  |

|     |          | syscall                                                                     |          |                  |                                    |  |  |  |  |  |

|     | read:    | li                                                                          | \$v0,    | 7                | #Syscall 7 for double read         |  |  |  |  |  |

|     |          | syscall                                                                     |          |                  |                                    |  |  |  |  |  |

| C)  |          | li.d                                                                        | \$f1     | 0, -1.0e0        | #sentinel                          |  |  |  |  |  |

|     |          | c.eq.d                                                                      | \$f0     | , \$f10          | # double comparison                |  |  |  |  |  |

| H   |          |                                                                             |          |                  | #break on sentinel                 |  |  |  |  |  |

|     |          | lw                                                                          | \$a0     | HEAD(\$zero)     | #a0 points to first node           |  |  |  |  |  |

| 2   | #        | add                                                                         | Şa1,     | \$v0, \$zero     | #f0 has read int                   |  |  |  |  |  |

| ЧÇ, |          | jal                                                                         | insdCel  | 1                |                                    |  |  |  |  |  |

| 83  |          | SW                                                                          | \$v0,    | HEAD(\$zero)     | #HEAD points to last node          |  |  |  |  |  |

|     |          | j                                                                           | prompt   |                  | #continue                          |  |  |  |  |  |

|     | endRead: | ### End                                                                     | of read  | ing and processi | ng ints                            |  |  |  |  |  |

| lw       | \$a0,                   | HEAD(\$zero)                         |                                                           |                                                                           |

|----------|-------------------------|--------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------|

| jal      | printdLi                | .st                                  |                                                           |                                                                           |

| addi     | \$sp,                   | 4                                    | #wrapping w                                               | up main                                                                   |

| lw       | \$ra,                   | 0(\$sp)                              |                                                           |                                                                           |

| jr       | \$ra                    |                                      |                                                           |                                                                           |

| # End of | main                    |                                      |                                                           |                                                                           |

|          | jal<br>addi<br>lw<br>jr | jal printdLi<br>addi Şsp,<br>lw Şra, | jal printdList<br>addi Şsp, 4<br>lw Şra, O(Şsp)<br>jr Şra | jal printdList<br>addi \$sp, 4 #wrapping w<br>lw \$ra, 0(\$sp)<br>jr \$ra |

## Lab D – Double Precision Read/Write (cont'd)

####

|              | # insd   |           |               |                                  |                  |         |          |           |          |                             |    |

|--------------|----------|-----------|---------------|----------------------------------|------------------|---------|----------|-----------|----------|-----------------------------|----|

|              |          |           | ew node and s | tores the passed parameter in it |                  |         |          |           |          |                             |    |

|              |          | meters:   |               |                                  |                  |         |          |           |          |                             |    |

|              |          |           | ter to next   |                                  |                  |         |          |           |          |                             |    |

|              |          |           | le to be sto  | red                              |                  |         |          |           |          |                             |    |

|              | # Retu   |           |               |                                  |                  |         |          |           |          |                             |    |

|              | # \$v    | v0 = addr | ess of creat  | ed node                          |                  |         |          |           |          |                             |    |

|              | #        |           |               |                                  |                  |         |          |           |          |                             |    |

|              | #12-10   | )-23 - Mo | dified to in  | sert double precision values - H | .Chesser         |         |          |           |          |                             |    |

|              | ######   | *######## | *********     | ******                           | ##               |         |          |           |          |                             |    |

| insdCell     | add      | \$t0, \$  | zero, \$a0    |                                  |                  |         |          |           |          |                             |    |

|              | add      | \$t1, \$  | zero, Şal     |                                  |                  |         |          |           |          |                             |    |

|              | li       | \$a0,     | 12            | #allocate 12 bytes - link        | address + double |         |          |           |          |                             |    |

|              | li       | \$v0,     | 9             |                                  |                  | ######  | ######## | ######### | *****    | ******                      | #  |

|              | syscal   | .1        |               |                                  |                  | # prin  |          |           | *****    |                             | π  |

|              | SW       | ŞtO,      | 0(\$v0)       | #save pointer                    |                  | _       |          | ontent of | f the li | nked list.                  |    |

|              | sdc1     | \$f0,     | 4(\$v0)       | #save double data                |                  |         | meters:  |           |          |                             |    |

|              | jr Şra   | L         |               |                                  |                  |         |          | ter first | t node   |                             |    |

|              |          |           |               |                                  |                  | #       | -        |           |          |                             |    |

|              | r        |           |               |                                  |                  | # 12-1  | 0-23 - M | odified t | to print | double values - H.Chesser   |    |

| × '          | 1        |           |               |                                  |                  | ######  | ######## | ########  | #######  | *****                       | #  |

|              |          |           |               |                                  | printdList       | : add   | \$t0,    | \$zero    | \$a0     |                             |    |

| Selet .      |          |           |               |                                  |                  | beq     | \$t0,    | \$zero    | endPri   | nt                          |    |

|              |          |           |               |                                  |                  | ldc1    | \$f12,   | 4(\$t0)   |          | #get data                   |    |

| E 8.         | <b>T</b> |           |               |                                  |                  | li      | \$v0,    | 3         |          | #Syscall 3 for double print |    |

|              | Cal      |           |               |                                  |                  | syscal  | 1        |           |          | #print                      |    |

|              | 76       |           |               |                                  |                  | li      | \$a0,    | 10        |          | #printnl                    |    |

| 6.0          |          |           |               |                                  |                  | li      | \$v0,    | 11        |          |                             |    |

| <b>1</b> - 1 | 44       |           |               |                                  |                  | syscal  | 1        |           |          |                             |    |

|              | 199      |           |               |                                  |                  | lw      | \$a0,    | 0(\$t0)   |          |                             |    |

|              | CZ.      |           |               |                                  |                  | j       | printd   | List      |          | #continue                   |    |

| 111          | + # }    |           |               |                                  | endPrint:        | jr \$ra |          |           |          |                             |    |

| Hat          | 634      |           |               |                                  |                  |         |          |           |          |                             |    |

|              | Y. / 1   |           |               |                                  | ₩ <b>₽-</b> ₩    |         |          |           |          |                             | 20 |