#### What is an HDL?

A Hardware Description Language (HDL) is a software programming language used to model the intended operation of a piece of hardware.

- The difference between an HDL and "C"

Concurrency

- Timing

- A powerful feature of the Verilog HDL is that we can use the same language for describing, testing and debugging the system.

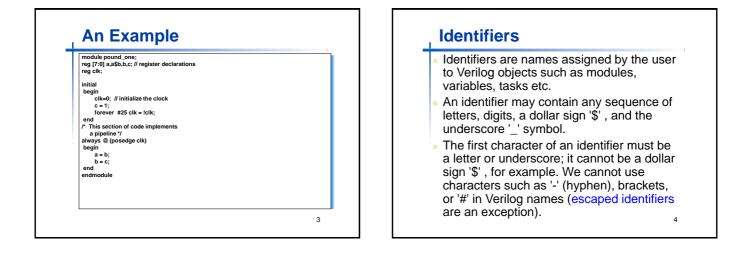

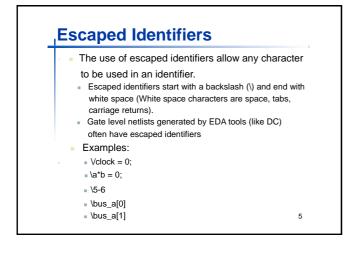

|                         | module identifiers; /* Multiline comments in Verilog Iook like C comment<br>and // is OK in here. */ | s |

|-------------------------|------------------------------------------------------------------------------------------------------|---|

|                         | // Single-line comment in Verilog.                                                                   |   |

|                         | reg legal_identifier, twounderscores;                                                                |   |

| <mark>9</mark>          | reg _OK,OK_,OK_\$,OK_123,CASE_SENSITIVE, case_sensitive;                                             |   |

|                         | reg Vclock ,\a*b ; // Add white_space after escaped identifier.                                      |   |

|                         | <pre>//reg \$_BAD,123_BAD; // Bad names even if we declare them! initial begin</pre>                 |   |

|                         | legal_identifier = 0; // Embedded underscores are OK,                                                |   |

| <mark>An Example</mark> | two_underscores = 0; // even two underscores in a row.                                               |   |

| E                       | _OK = 0; // Identifiers can start with underscore                                                    |   |

| X                       | OK_ = 0; // and end with underscore.                                                                 |   |

| ш                       | OK\$ = 0; // \$ sign is OK.                                                                          |   |

| La la                   | OK_123 =0; // Embedded digits are OK.                                                                |   |

|                         | CASE_SENSITIVE = 0; // Verilog is case-sensitive (unlike VHDL).<br>case sensitive = 1:               |   |

|                         | Vclock = 0; // An escaped identifier with \ breaks rules                                             |   |

|                         | $a^{b} = 0$ ; // but be careful to watch the spaces!                                                 |   |

|                         | \$display("Variable CASE_SENSITIVE= %d",CASE_SENSITIVE);                                             |   |

|                         | \$display("Variable case sensitive= %d",case sensitive);                                             |   |

|                         | \$display("Variable Vclock = %d", Vclock );                                                          |   |

|                         | \$display("Variable \\a*b = %d",\a*b );                                                              |   |

|                         | end                                                                                                  |   |

|                         | endmodule                                                                                            | 6 |

|                         |                                                                                                      |   |

#### Simulation Result of the Example

Variable CASE\_SENSITIVE= 0 Variable case\_sensitive= 1 Variable /clock = 0 Variable \a\*b = 0

## **Logic values**

Verilog has 4 logic Values:

- '0' represents zero, low, false, not asserted.

- '1' represents one, high, true, asserted.

- 'z' or 'Z' represent a high-impedance

- value, which is usually treated as an 'x' value. • 'x' or 'X' represent an uninitialized or an

- unknown logic value--an unknown value is either '1', '0', 'z', or a value that is in a state of change.

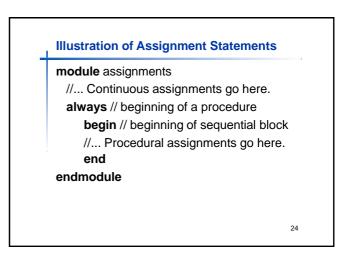

# **Procedural Blocks**

- There are two types of procedural blocks:

- initial blocks executes only once

- always blocks executes in a loop

- Multiple Procedural blocks may be used, if so the multiple blocks are *concurrent*.

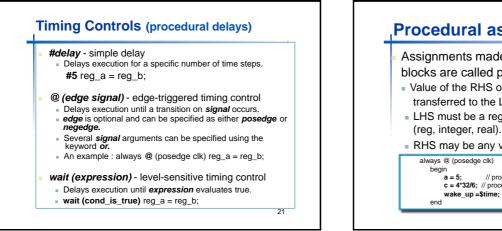

- Procedural blocks may have:

- Timing controls which delays when a statement may be executed

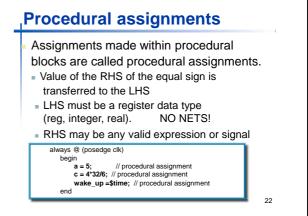

- Procedural assignments

- Programming statements

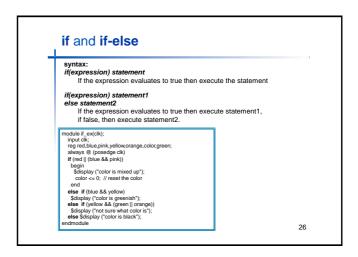

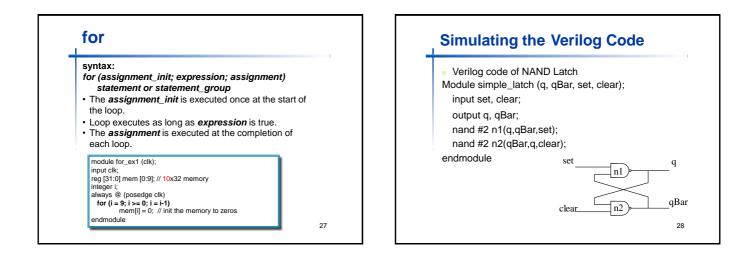

## **Control Statements**

- Two types of programming statements:

- Conditional

- Looping

- Programming statements only used in procedural blocks