# EECS 3201: Digital Logic Design Lecture 11

Ihab Amer, PhD, SMIEEE, P.Eng.

# II. Design of Sequential Circuits

Given the word description and specs of the desired operation, obtain the state diagram/table of the circuit, and hence derive the circuit diagram

#### Example 1

#### Using D-type FFs, design a circuit that detects three or more consecutive 1's in a stream of bits coming through an input line

Four States ----> Two FF's

#### Assuming binary state encoding

| Required States                                                 |                                  |      |      |

|-----------------------------------------------------------------|----------------------------------|------|------|

| No cons. 1's detected so far $\longrightarrow$ S <sub>0</sub>   | State                            | FF o | o/ps |

| First cons. 1 detected so far $\longrightarrow$ S <sub>1</sub>  |                                  | Α    | В    |

|                                                                 | S <sub>0</sub>                   | 0    | 0    |

| Two cons. 1's detected so far $\longrightarrow$ S <sub>2</sub>  | S <sub>1</sub><br>S <sub>2</sub> | 0    | 1    |

| Three (or more) cons. 1's detected so far $\longrightarrow S_3$ | $S_2$<br>$S_3$                   | 1    | 1    |

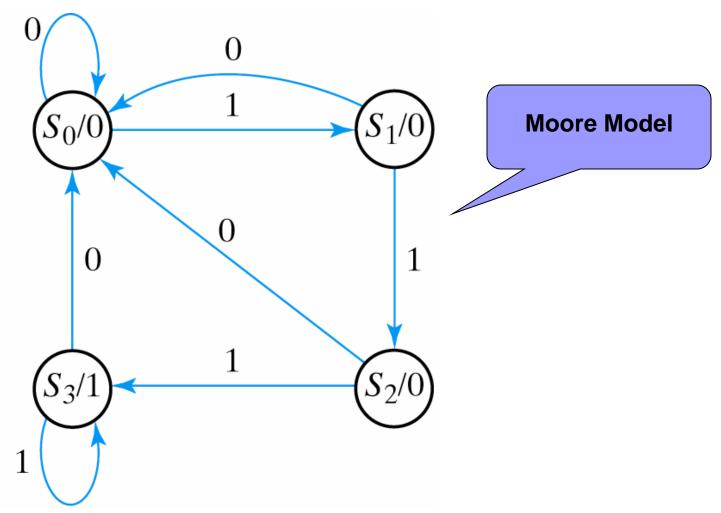

#### State Diagram

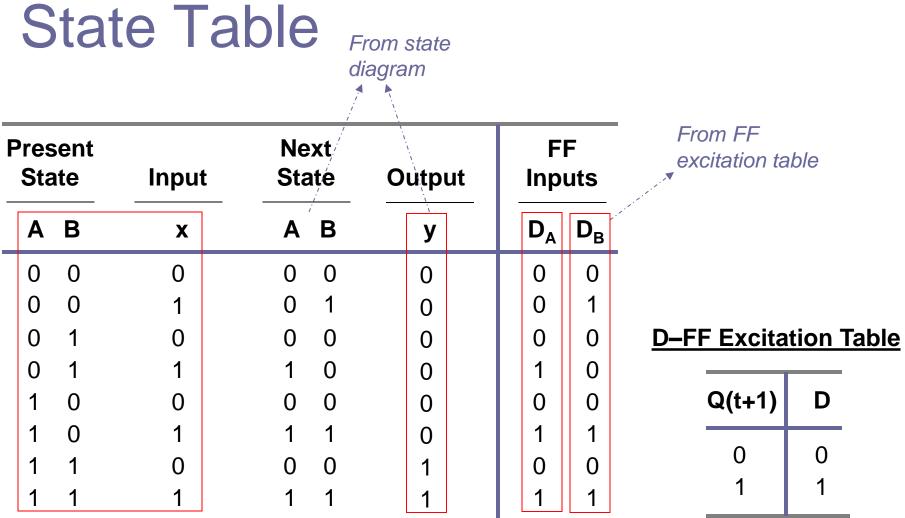

FF(s) Input/Output Equation(s):

$$D_A(A, B, x) = \sum(3, 5, 7)$$

$$D_B(A, B, x) = \sum(1, 5, 7)$$

$$y(A, B, x) = \sum(6, 7)$$

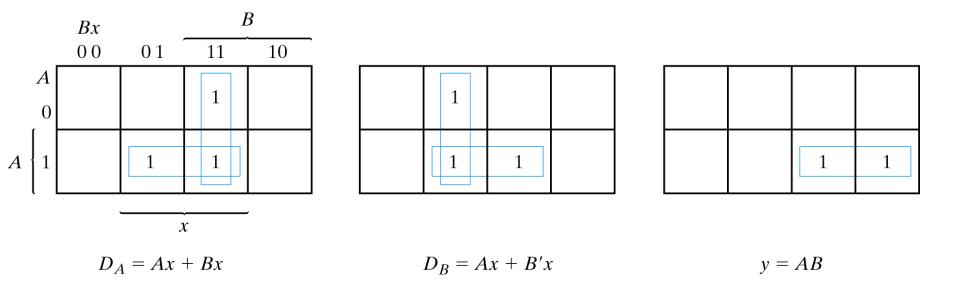

# K-Maps for FF Input(s)

FF(s) Input/Output Equation(s):

$\begin{array}{l} \mathsf{D}_{\mathsf{A}}(\mathsf{A},\,\mathsf{B},\,\mathsf{x})=\sum(3,\,5,\,7)\\ \mathsf{D}_{\mathsf{B}}(\mathsf{A},\,\mathsf{B},\,\mathsf{x})=\sum(1,\,5,\,7)\\ \mathsf{y}(\mathsf{A},\,\mathsf{B},\,\mathsf{x})=\sum(6,\,7) \end{array}$

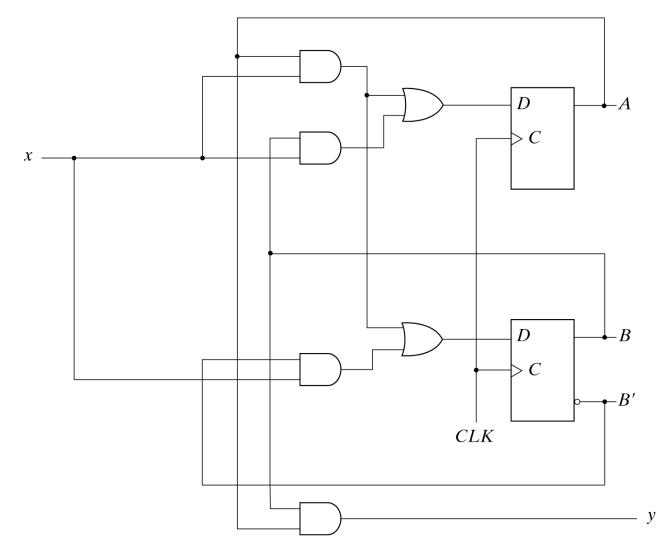

# Circuit (Logic) Diagram

7

#### Another State Encoding Technique

- Binary encoding uses the min possible number of FF's to store the state, however additional logic is required to encode or decode the state

- One-hot encoding is another state encoding technique, where only one bit of the "state vector" is set for any given state

n states → n FF's

# **One-hot Vs Binary Encoding**

- Faster

- Speed independent of the # of states

- Easier to design/code the FSM

- Adding/deleting states is easier

- Easier debugging

#### Binary

Slightly Cheaper

YORK

- Slower as the # of states gets larger

- More effort to design/code the FSM

- Adding/deleting states affects the rest of the machine

- More difficult debugging

#### **Practice Assignment**

Solve the previous example using one-hot state encoding rather than binary state encoding

#### Example 2

# Using JK-FF(s), design the logic circuit that corresponds to the following state table

| Present<br>State Input |   | Next<br>State |   |   | Fl<br>Inpu     |                |                | From FF<br>excitation table |        |         |     |       |

|------------------------|---|---------------|---|---|----------------|----------------|----------------|-----------------------------|--------|---------|-----|-------|

| Α                      | В | x             | Α | В | J <sub>A</sub> | K <sub>A</sub> | J <sub>B</sub> | K <sub>B</sub>              | .IK-FF | Excitat | ion | Table |

| 0                      | 0 | 0             | 0 | 0 | 0              | Х              | 0              | Х                           |        |         |     |       |

| 0                      | 0 | 1             | 0 | 1 | 0              | Х              | 1              | Х                           | Q(t)   | Q(t+1)  | J   | κ     |

| 0                      | 1 | 0             | 1 | 0 | 1              | Х              | Х              | 1                           |        |         |     |       |

| 0                      | 1 | 1             | 0 | 1 | 0              | Х              | Х              | 0                           | 0      | 0       | 0   | Х     |

| 1                      | 0 | 0             | 1 | 0 | X              | 0              | 0              | Х                           | 0      | 1       | 1   | Х     |

| 1                      | 0 | 1             | 1 | 1 | X              | 0              | 1              | Х                           | 1      | 0       | Х   | 1     |

| 1                      | 1 | 0             | 1 | 1 | Х              | 0              | Х              | 0                           | 1      | 1       | Х   | 0     |

| 1                      | 1 | 1             | 0 | 0 | Х              | 1              | Х              | 1                           |        |         |     | 11    |

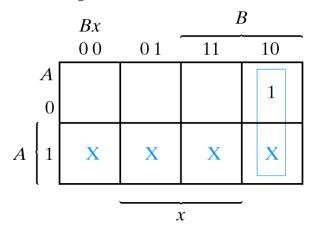

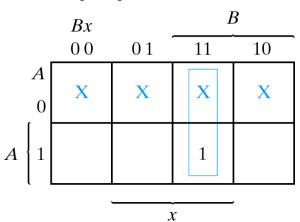

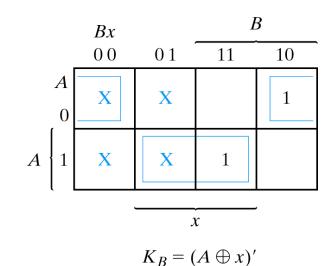

#### K-Maps for FF Input(s)

$$J_A = Bx'$$

$K_A = Bx$

BBx 0001 11 10 A Χ Х 1 0 Χ  $\boldsymbol{A}$ Х 1 1 х

$J_B = x$

12

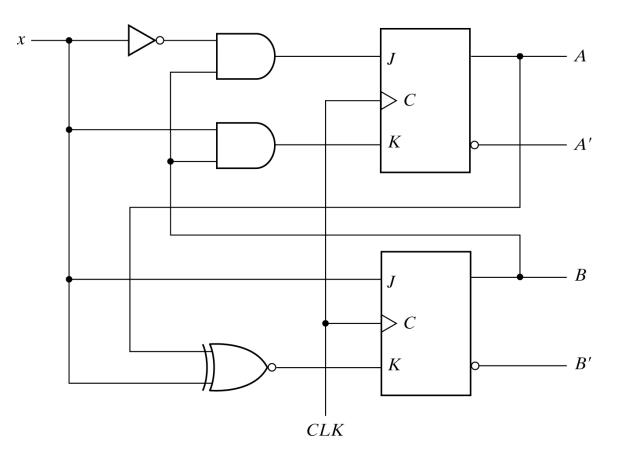

# Circuit (Logic) Diagram

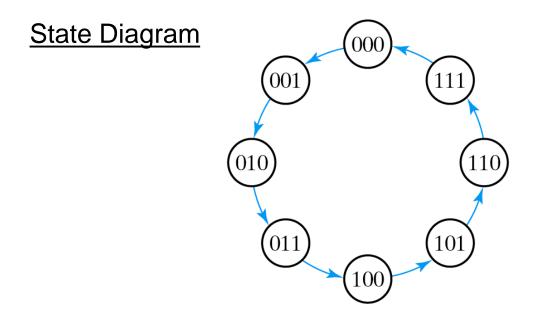

#### Example 3

#### Using T-type FFs, design a 3-bits binary counter that can count in binary from 0 to 7

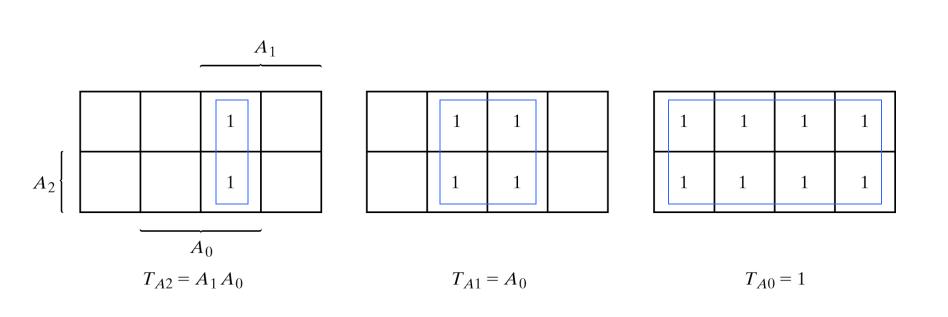

#### State Table

|                       | ese<br>State          |                | _              | Nex<br>Stat |                |   |         | FF<br>puts      | ;               | _        | From FF<br>excitation table |           |          |

|-----------------------|-----------------------|----------------|----------------|-------------|----------------|---|---------|-----------------|-----------------|----------|-----------------------------|-----------|----------|

| <b>A</b> <sub>2</sub> | <b>A</b> <sub>1</sub> | A <sub>0</sub> | A <sub>2</sub> | A           | A <sub>0</sub> | 1 | -<br>A2 | T <sub>A1</sub> | T <sub>A0</sub> | _        |                             |           |          |

| 0                     | 0                     | 0              | 0              | 0           | 1              |   | )       | 0               | 1               | - т      |                             | Typitatio | n Tabla  |

| 0                     | 0                     | 1              | 0              | 1           | 0              |   | C       | 1               | 1               | <u>1</u> |                             | Excitatio |          |

| 0                     | 1                     | 0              | 0              | 1           | 1              |   | C       | 0               | 1               |          | Q(t)                        | Q(t+1)    | т        |

| 0                     | 1                     | 1              | 1              | 0           | 0              |   | 1       | 1               | 1               |          |                             | α(ι+1)    | <b>_</b> |

| 1                     | 0                     | 0              | 1              | 0           | 1              |   | C       | 0               | 1               |          | 0                           | 0         | 0        |

| 1                     | 0                     | 1              | 1              | 1           | 0              |   | C       | 1               | 1               |          | 0                           | 1         | 1        |

| 1                     | 1                     | 0              | 1              | 1           | 1              |   | C       | 0               | 1               |          | 1                           | 0         | 1        |

| 1                     | 1                     | 1              | 0              | 0           | 0              |   | 1       | 1               | 1               | _        | 1                           | 1         | 0        |

#### K-Maps for FF Input(s)

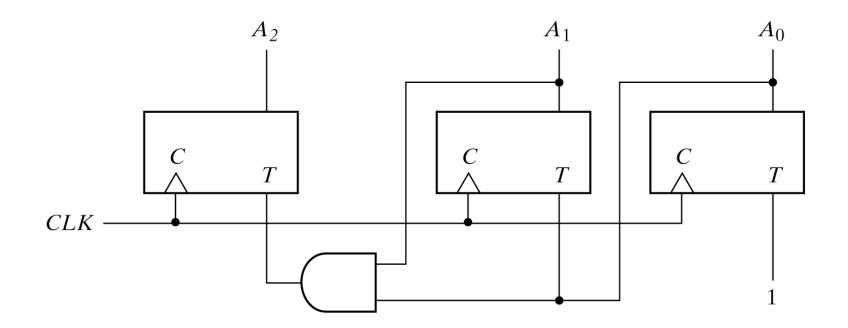

# Circuit (Logic) Diagram

17

#### Important Book Chapter

#### Chapter 5 in textbook

#### Guidelines for the Midterm

Please read carefully before proceeding.

- 1. The duration of this exam is 90 minutes.

- 2. Point value of this exam is tentatively (30%).

- 3. Only un-programmable calculators are permitted for this exam.

4. You can use the back and/or the front of any exam sheet(s) (except pages 1-3) for your scratch.

5. The exam consists of EIGHTEEN multiple choice questions, in SIXTEEN pages (including the cover page). Please inform your proctor if you have any missing page(s) or question(s). You will lose the grade of any question(s) that are located in missing page(s).

#### **Exam Strategy**

Please insert all your answers for the exam in the table(s) that are provided in the next page. Your grade in this exam will depend <u>only</u> on the answers that are indicated in the table(s). Tick (or cross) the table cell that corresponds to the answer that you believe is the most suitable.

#### More Guidelines

- a. If you solve any 15 out of the 18 questions correctly, you will get 100% of the total grade.

- b. Read all the *questions* <u>carefully</u>. For problems where Verilog HDL code is provided, pay attention to the comments inside the code and the modules' names.

- c. Read all the *choices* <u>carefully</u>. There are choices that "<u>look</u>" alike, however they are obviously not!

- d. This exam is designed so that the questions cover a broad range of difficulty-levels. Manage your time so that you do not lose the grades of the relatively-easy questions because of getting stuck at relatively-difficult questions.

- e. Unless otherwise can be read from the waveforms, assume that shaded/patterned parts correspond to don't cares (X: unknowns).

- f. Assume the existence of the following statement before all the given Verilog HDL modules: `timescale 1ns / 1ps

# Exam Style!

- Broad selection of MCQ's based on topics delivered in lectures 1-8

- Various types of problems

- Theory

- Problems to assess understanding of theoretical principles provided

- Lots of Verilog! Maybe in the question(s) or the answer(s)!

- Lots of Timing Simulations! Maybe in the question(s) or the answer(s)!

#### Final Advice!

- Read question(s) well

- Read all choices. Pay attention to "None of the previous", "All of the previous", (i) and (ii), etc.

- Think first, don't bang your head against the wall

- Good Luck!

#### References

- Digital Design, M. Morris, Mano

- http://bawankule.com/verilogfaq/files/jhld099401. pdf