### EECS 3201: Digital Logic Design Lecture 12

Ihab Amer, PhD, SMIEEE, P.Eng.

#### Registers

- Collections of flip-flops with special controls and logic

- Stored values somehow related (e.g., form binary value)

- □ Share clock, reset, and set lines

#### Examples

- □ Shift registers

- Counters

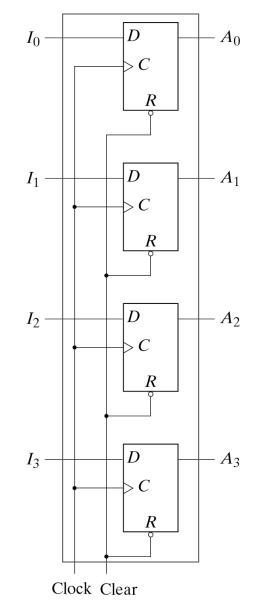

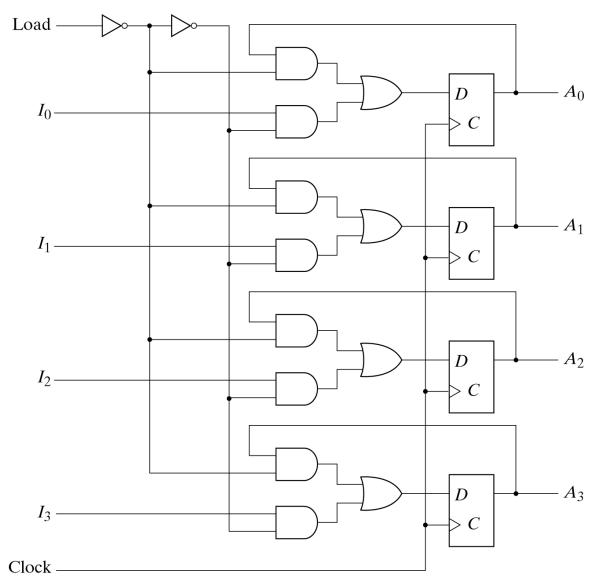

#### Four-bits Register

- Parallel load

- Clock must be inhibited from the circuit if the contents of the register is to be left unchanged (enabling gate)

- Performing logic with clock pulses inserts variable delays and may cause the system to go out of synchronism

- <u>Solution</u>: Direct the load control input through gates and into the FF inputs

### Registers with Parallel Load YORK

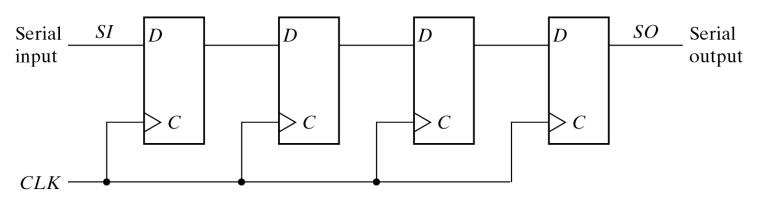

### **Shift Registers**

A Register capable of shifting its content in one or both directions is called a shift register. It has many applications such as serial transfer and serial addition

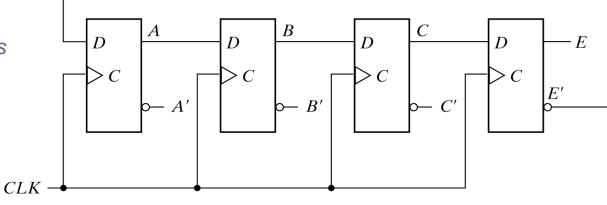

Serial-In/Serial-Out 4-bit shift register

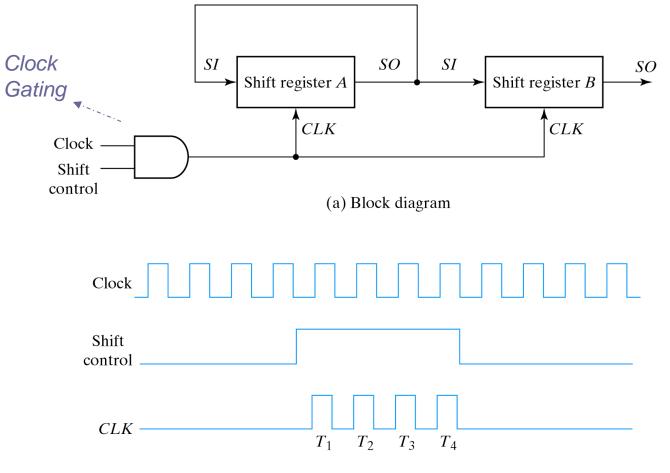

#### **Serial Transfer**

(b) Timing diagram

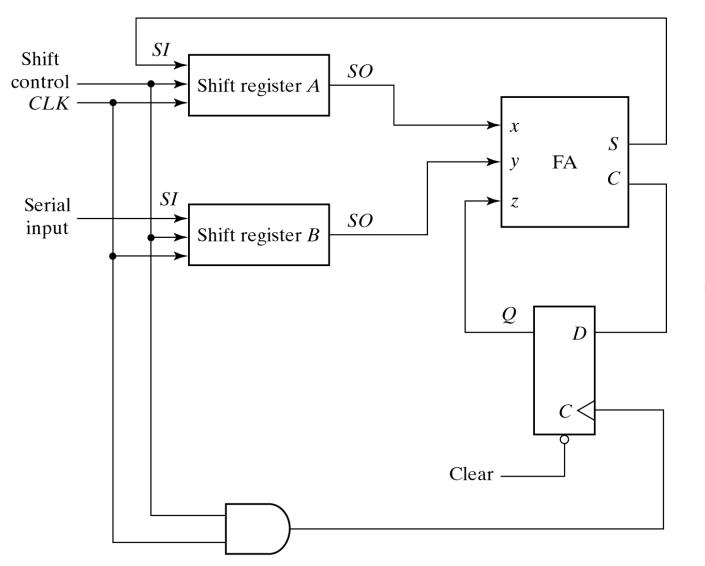

#### **Serial Adder**

Refer to the textbook for the *design* of another form of a serial adder using JK FF

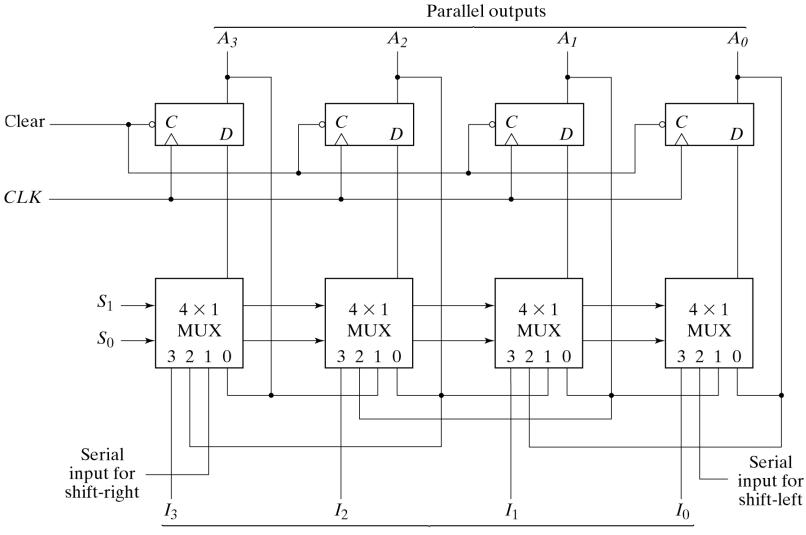

#### **Universal Shift Register**

Parallel inputs

### HDL for U Shift Register

| Mode<br>Control       |                | Register<br>Operation |  |

|-----------------------|----------------|-----------------------|--|

| <b>S</b> <sub>1</sub> | S <sub>0</sub> | operation             |  |

| 0                     | 0              | No Change             |  |

| 0                     | 1              | Shift Right           |  |

| 1                     | 0              | Shift Left            |  |

| 1                     | 1              | Parallel Load         |  |

**module** shftreg (s1,s0,Pin,Ifin,rtin,A,CLK,Clr); input s1,s0; //Select inputs **input** lfin, rtin; //Serial inputs //Clock and Clear input CLK,Clr; **input** [3:0] Pin; //Parallel input output [3:0] A; //Register output **reg** [3:0] A; always @ (posedge CLK or negedge Clr) if ( $\sim$ Clr) A = 4'b0000; else **case** ({s1,s0}) 2'b00: A = A; //No change 2'b01: A = {rtin,A[3:1]}; //Shift right 2'b10: A = {A[2:0], Ifin}; //Shift left 2'b11: A = Pin; //Parallel load input endcase endmodule 9

### **Structural Description**

```

module SHFTREG

(I,select,lfin,rtin,A,CLK,Clr);

input [3:0] l;

//Parallel input

input [1:0] select; //Mode select

input lfin,rtin,CLK,Clr; //Serial

//inputs.clock.clear

output [3:0] A;

//Parallel output

//Instantiate the four stages

stage ST0

(A[0],A[1],Ifin,I[0],A[0],select,CLK,Clr);

stage ST1

(A[1], A[2], A[0], I[1], A[1], select, CLK, Clr);

stage ST2

(A[2], A[3], A[1], I[2], A[2], select, CLK, Clr);

stage ST3

(A[3],rtin,A[2],I[3],A[3],select,CLK,Clr);

endmodule

```

```

module stage(i0,i1,i2,i3,Q,select,CLK,Clr);

input i0,i1,i2,i3,CLK,Clr;

input [1:0] select;

output Q;

reg Q;

reg D;

//4x1 multiplexer

always @ (i0 or i1 or i2 or i3 or select)

case (select)

2'b00: D = i0:

2'b01: D = i1;

2'b10: D = i2;

2'b11: D = i3;

endcase

//D flip-flop

always @ (posedge CLK or negedge Clr)

if (\simClr) Q = 1'b0;

else Q = D:

endmodule

10

```

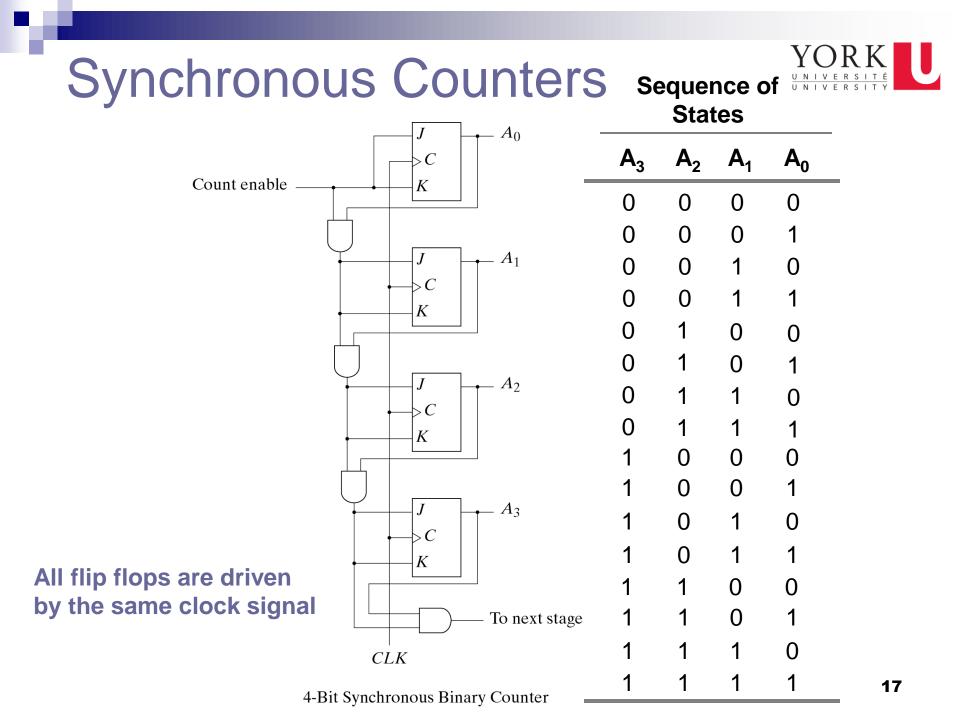

#### Counters

- A register that goes through a prescribed sequence of states upon the application of input pulses is called a counter

- Examples of counters are ripple and synchronous counters

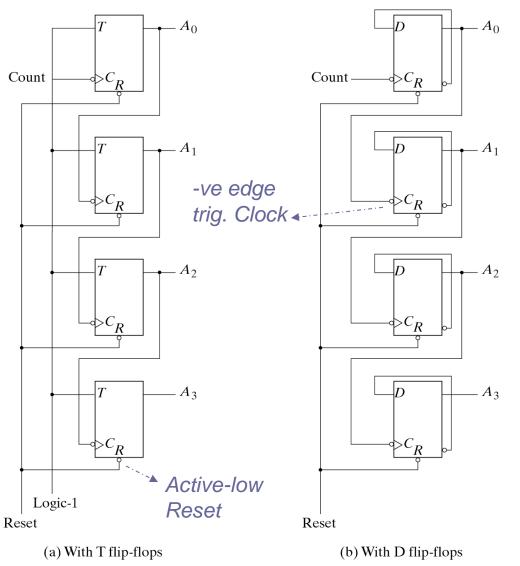

#### **Ripple Counters**

| _ | Se                    | quen<br>Stat          | ice of<br>es          | YO<br>UNIVE    | RK<br>RSITÉ<br>RSITY |

|---|-----------------------|-----------------------|-----------------------|----------------|----------------------|

|   | <b>A</b> <sub>3</sub> | <b>A</b> <sub>2</sub> | <b>A</b> <sub>1</sub> | A <sub>0</sub> |                      |

|   | 0                     | 0                     | 0                     | 0              |                      |

|   | 0                     | 0                     | 0                     | 1              |                      |

|   | 0                     | 0                     | 1                     | 0              |                      |

|   | 0                     | 0                     | 1                     | 1              |                      |

|   | 0                     | 1                     | 0                     | 0              |                      |

|   | 0                     | 1                     | 0                     | 1              |                      |

|   | 0                     | 1                     | 1                     | 0              |                      |

|   | 0                     | 1                     | 1                     | 1              |                      |

|   | 1                     | 0                     | 0                     | 0              |                      |

|   | 1                     | 0                     | 0                     | 1              |                      |

|   | 1                     | 0                     | 1                     | 0              |                      |

|   | 1                     | 0                     | 1                     | 1              |                      |

|   | 1                     | 1                     | 0                     | 0              |                      |

|   | 1                     | 1                     | 0                     | 1              |                      |

|   | 1                     | 1                     | 1                     | 0              |                      |

|   | 1                     | 1                     | 1                     | 1              | 12                   |

4-Bit Binary Ripple Counter

### HDL for ripple counter

**module** ripplecounter (A0,A1,A2,A3,Count,Reset); **output** A0,A1,A2,A3; **input** Count, Reset; //Instantiate complementing flip-flop CF F0 (A0,Count,Reset); CF F1 (A1,A0,Reset); CF F2 (A2,A1,Reset); CF F3 (A3,A2,Reset); endmodule //Complementing flip-flop with delay //Input to D flip-flop = Q'**module** CF (Q,CLK,Reset); output Q; input CLK,Reset; Active-low Active-high Clock Reset reg Q; always @ (negedge CLK or posedge Reset) if (Reset) Q = 1'b0; else  $Q = #2 (\sim Q)$ ; // Delay of 2 time units endmodule

//Stimulus for testing ripple counter **module** testcounter: reg Count; **reg** Reset; wire A0, A1, A2, A3; //Instantiate ripple counter ripplecounter RC (A0,A1,A2,A3,Count,Reset); always #5 Count =  $\sim$ Count: initial begin Count = 1'b0; Reset = 1'b1; #4 Reset = 1'b0; #165 **\$finish**; end endmodule

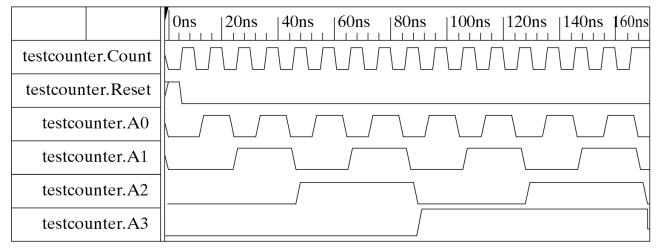

#### **Simulation Output**

(a) From 0 to 170 ns

|                   | 72ns 74ns 76ns 78ns 80ns 82ns 84ns 86ns 88ns 90ns 9 |

|-------------------|-----------------------------------------------------|

| testcounter.Count |                                                     |

| testcounter.Reset |                                                     |

| testcounter.A0    |                                                     |

| testcounter.A1    | 2 ns                                                |

| testcounter.A2    | ← - · · · · · ▶                                     |

| testcounter.A3    | ← - · · · · · ▶                                     |

|                   |                                                     |

(b) From 70 to 92 ns

Simulation Output of HDL Example 6-4

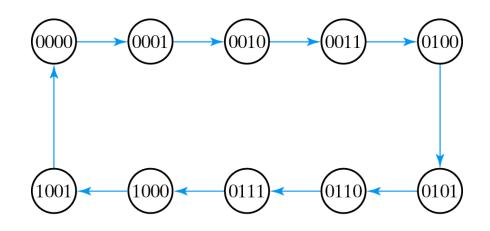

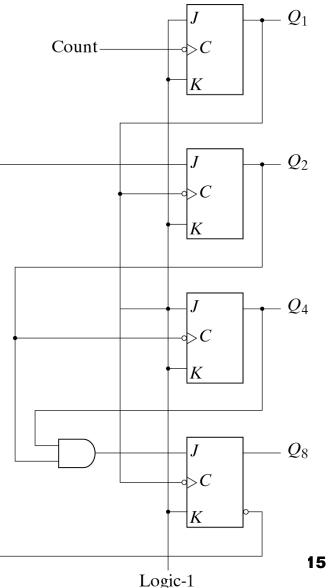

#### BCD Ripple Counter (self-study)

State Diagram of a Decimal BCD-Counter

- Q<sub>1</sub> changes after each clock pulse

- As long as Q<sub>8</sub> is 0, Q<sub>2</sub> complements each time Q<sub>1</sub> goes from 1 to 0

- Q<sub>2</sub> remains at 0 when Q<sub>8</sub> is 1

- Q<sub>4</sub> complements each time Q<sub>2</sub> goes from 1 to 0

- Q<sub>8</sub> remains at 0 as long as Q<sub>2</sub> or Q<sub>4</sub> is 0

- When both Q<sub>2</sub> and Q<sub>4</sub> are 1, Q<sub>8</sub> complements when Q<sub>1</sub> goes from 1 to 0

- Q<sub>8</sub> is cleared on the next -ve transition of Q<sub>1</sub>

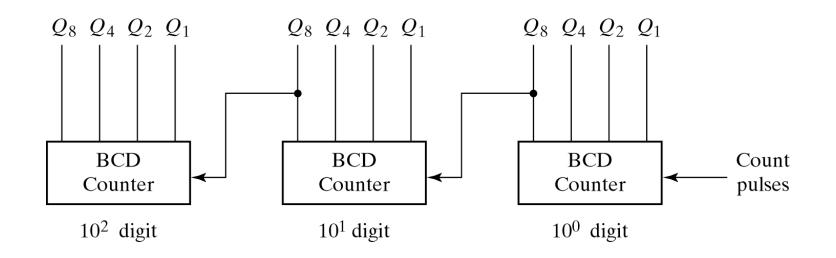

#### Three-Decade Decimal BCD Counter

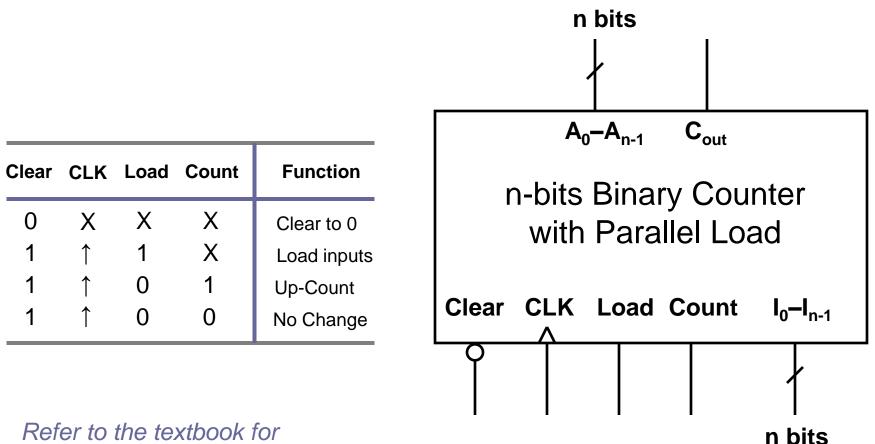

#### **Counter with Parallel Load**

Refer to the textbook for the circuit diagram

18

# HDL for Binary Counter with Parallel Load

```

module counter (Count,Load,IN,CLK,Clr,A,CO);

input Count,Load,CLK,Clr;

input [3:0] IN; //Data input

output CO;

//Output carry

output [3:0] A; //Data output

reg [3:0] A;

assign CO = Count & ~Load & (A == 4'b1111);

always @ (posedge CLK or negedge Clr)

if (\simClr) A = 4'b0000;

else if (Load) A = IN;

else if (Count) A = A + 1'b1;

else A = A; // no change, default condition

endmodule

```

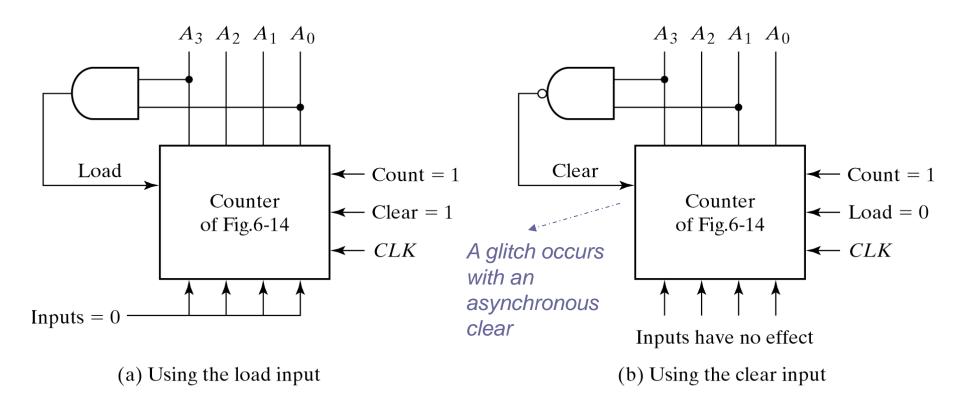

# BCD Counter using Counter with Parallel Load

Two ways to Achieve a BCD Counter Using a Counter with Parallel Load

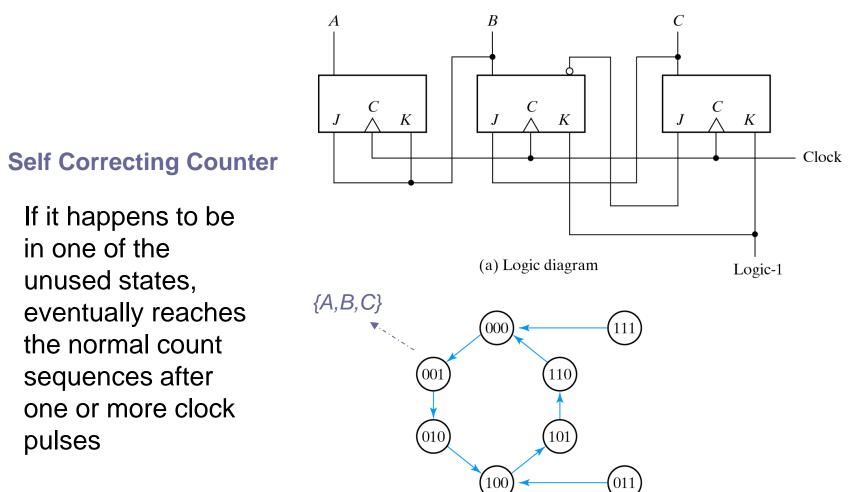

#### **Counter with Unused States**

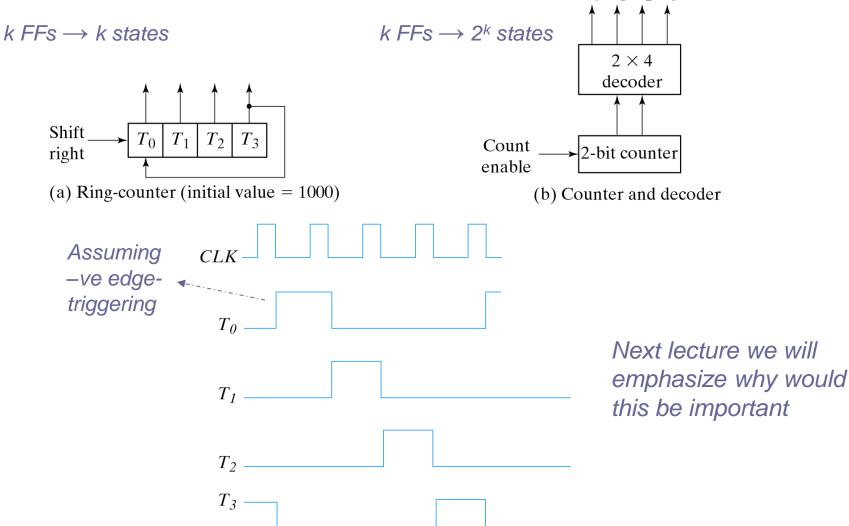

## Generating Timing Signals

<sup>(</sup>c) Sequence of four timing signals

#### Johnson Counter

$k FFs \rightarrow 2k$  states

(a) Four-stage switch-tail ring counter

| Sequence | Sequence Flip-flop outputs |   |   | ıts            | AND gate required |

|----------|----------------------------|---|---|----------------|-------------------|

| number   | Ā                          | В | С | $\overline{E}$ | for output        |

| 1        | 0                          | 0 | 0 | 0              |                   |

| 2        | 1                          | 0 | 0 | 0              | AB'               |

| 3        | 1                          | 1 | 0 | 0              | BC'               |

| 4        | 1                          | 1 | 1 | 0              | CE'               |

| 5        | 1                          | 1 | 1 | 1              | AE                |

| 6        | 0                          | 1 | 1 | 1              | A'B $	au$         |

| 7        | 0                          | 0 | 1 | 1              |                   |

| 8        | 0                          | 0 | 0 | 1              | C'E               |

(b) Count sequence and required decoding

Construction of a Johnson Counter

# Corresponding Chapter in Textbook

Chapter 6 (entire chapter)

#### References

- Digital Design, M. Morris, Mano

- http://bawankule.com/verilogfaq/files/jhld099401. pdf