# EECS 3201: Digital Logic Design Lecture 7

Ihab Amer, PhD, SMIEEE, P.Eng.

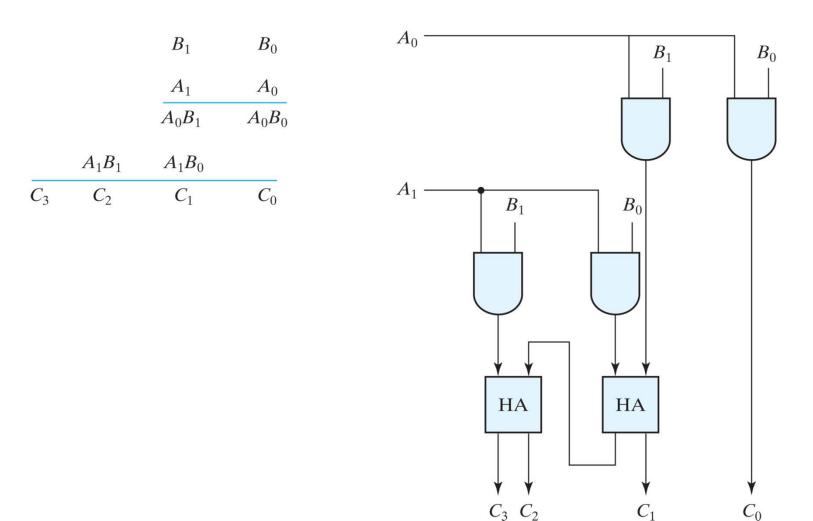

#### 2x2 binary multiplier

2

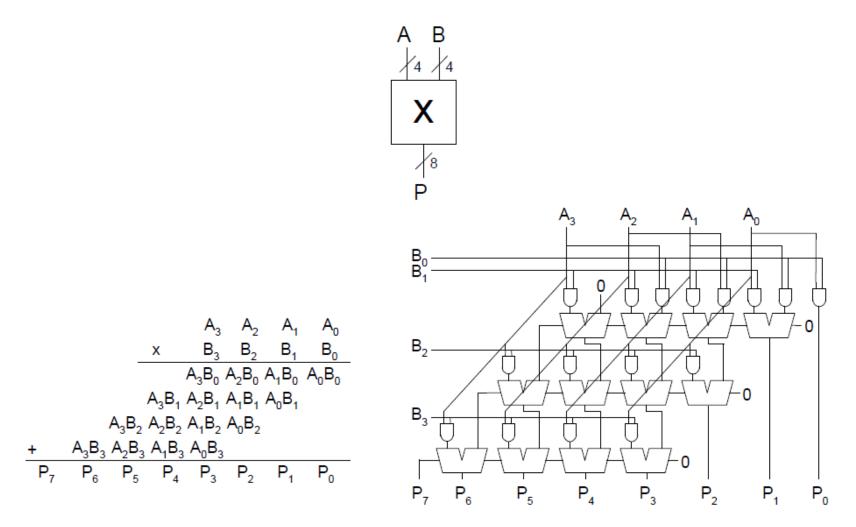

#### 4x4 Array Multiplier

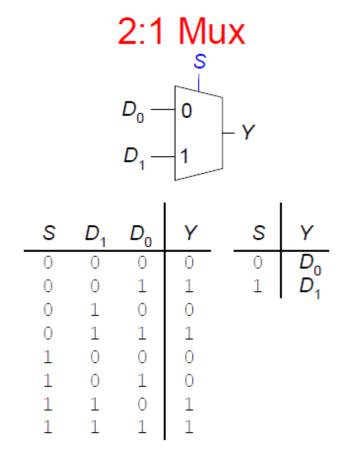

## Multiplexer (MUX)

- Selects between one of N inputs to connect to output

- log<sub>2</sub>N-bit select input control input

- Example:

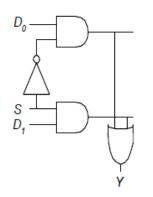

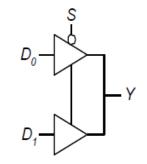

## **MUX Implementations**

- Logic gates

- sum-of-products form

- Tristates

- for an N-input mux, use N tristates

- turn on exactly one to select an appropriate input

### Wider MUXes

- Any of a number of options

- depends on technology

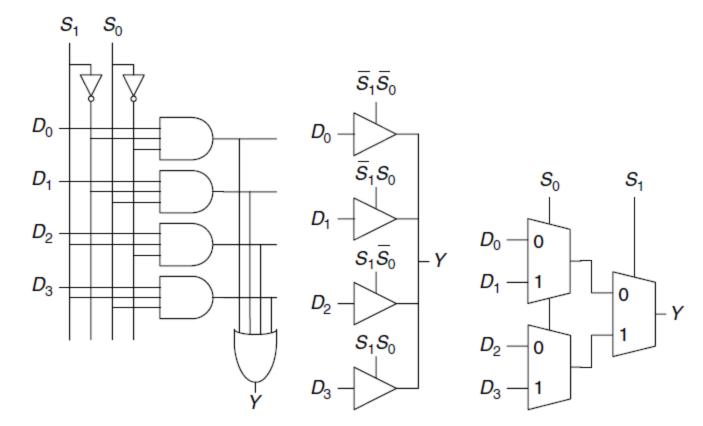

# Logic with MUXes

- Using the mux as a look-up-table

- N-input logic gate can be represented with a 2<sup>N</sup> input mux

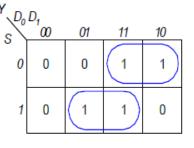

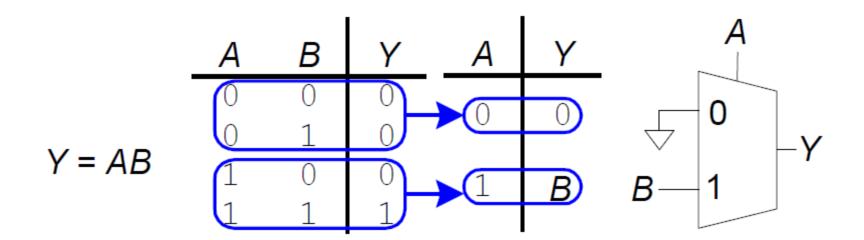

# Reducing the MUX Size

- Actually...

- N-input logic gate can be represented with a 2<sup>N-1</sup> mux

- Provide one of the literals as an input

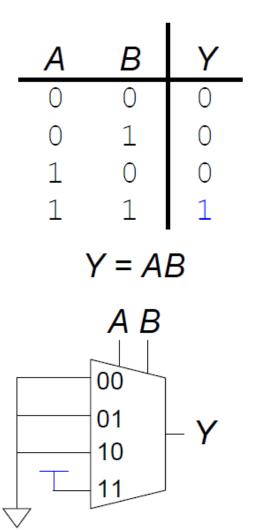

#### Mux this!

| A | В | С | Y |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

$Y = A\overline{B} + \overline{B}\overline{C} + \overline{A}BC$

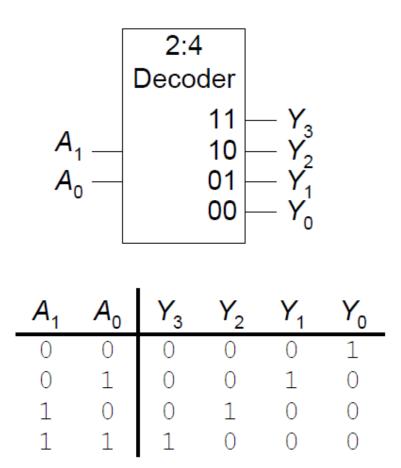

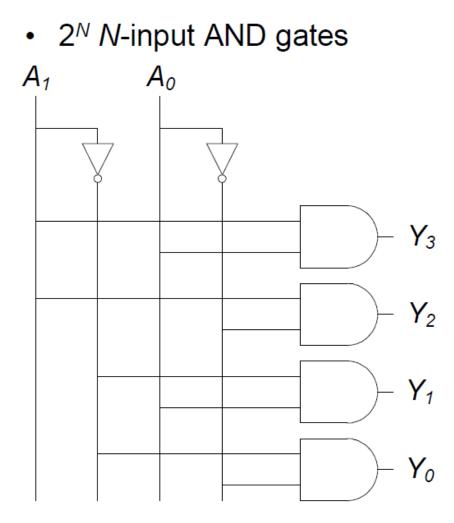

#### Decoders

- *N* inputs, 2<sup>*N*</sup> outputs

- One-hot outputs: only one output HIGH at once

#### **Decoder Implementation**

| A | $A_0$            | <i>Y</i> <sub>3</sub> | <i>Y</i> <sub>2</sub> | <i>Y</i> <sub>1</sub> | <i>Y</i> <sub>0</sub> |

|---|------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| 0 | 0                | 0                     | 0                     | 0                     | 1                     |

| 0 | 1                | 0                     | 0                     | 1                     | 0                     |

| 1 | 0                | 0                     | 1                     | 0                     | 0                     |

| 1 | 0<br>1<br>0<br>1 | 1                     | 0                     | 0                     | 0                     |

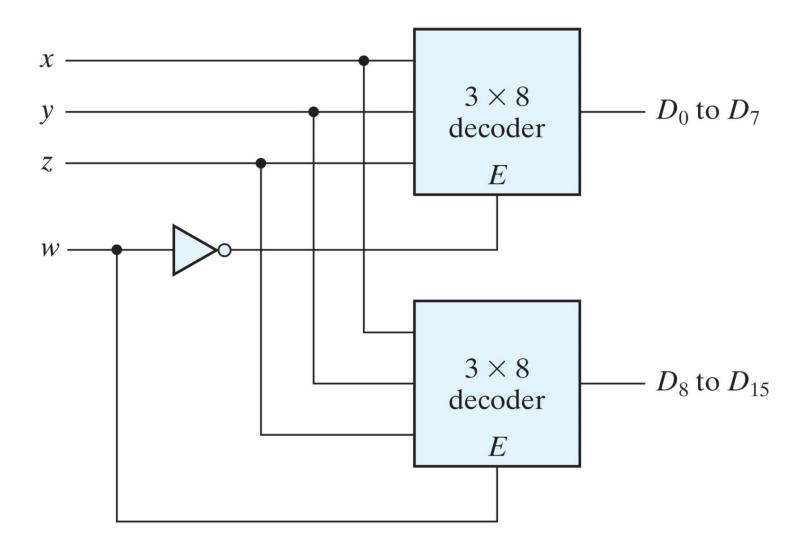

#### 4x16 Decoder out of 3x8 ones

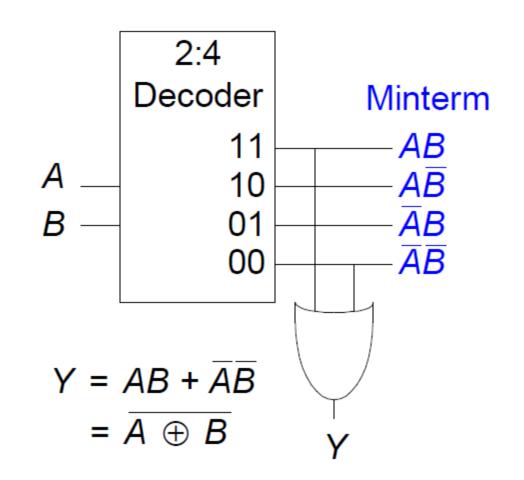

# Logic Using Decoders

OR minterms

### Memory

- Most real-world digital systems do contain one or more memory units

- A memory unit is a device to which binary information is transferred for storage and from which information is retrieved when needed for processing

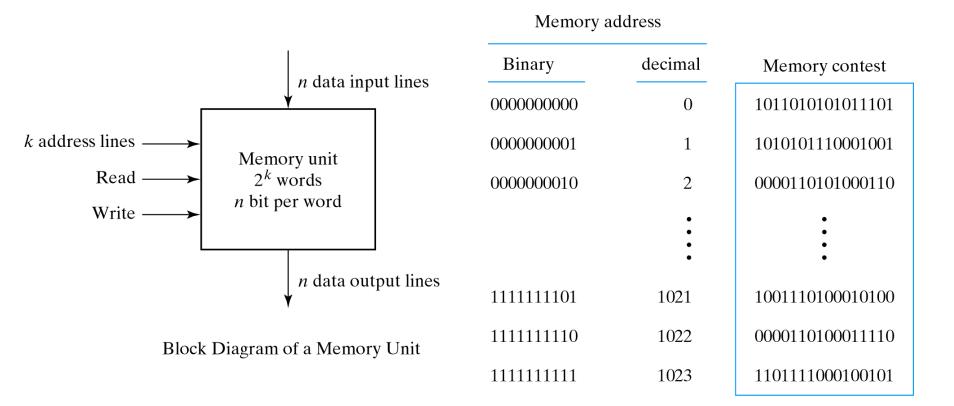

#### Random-Access Memory (RAM)

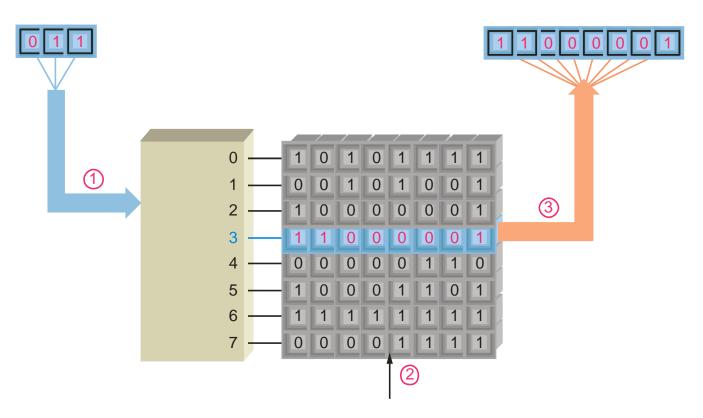

Content of a  $1024 \times 16$  Memory

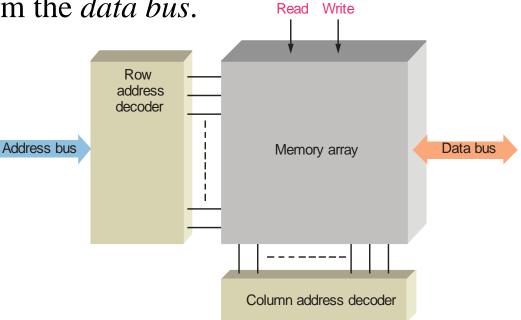

## Memory Addressing

In order to read or write to a specific memory location, a binary code is placed on the *address bus*. Internal decoders decode the address to determine the specific location. Data is then moved to or from the *data bus*.

The address bus is a group of conductors with a common function. Its size determines the A number of locations that can be accessed. A 32 bit address bus can access 2<sup>32</sup> locations, which is approximately 4G.

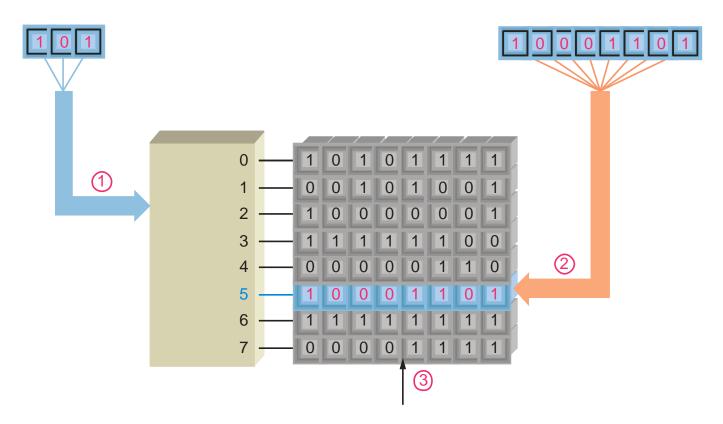

#### Illustration of the Write Operation

- 1. The address is placed on the address bus.

- 2. Data is placed on the data bus.

- 3. A write command is issued.

#### Illustration of the Read Operation

- 1. The address is placed on the address bus

- 2. A read command is issued

- 3. A copy of the data is placed in the data bus and shifted into the data register

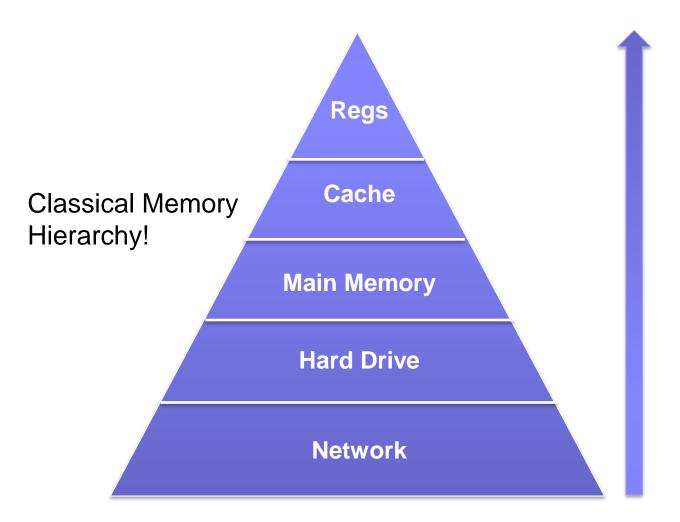

## Memory Speed Vs Cost

Better Performance per WATT & Higher Cost

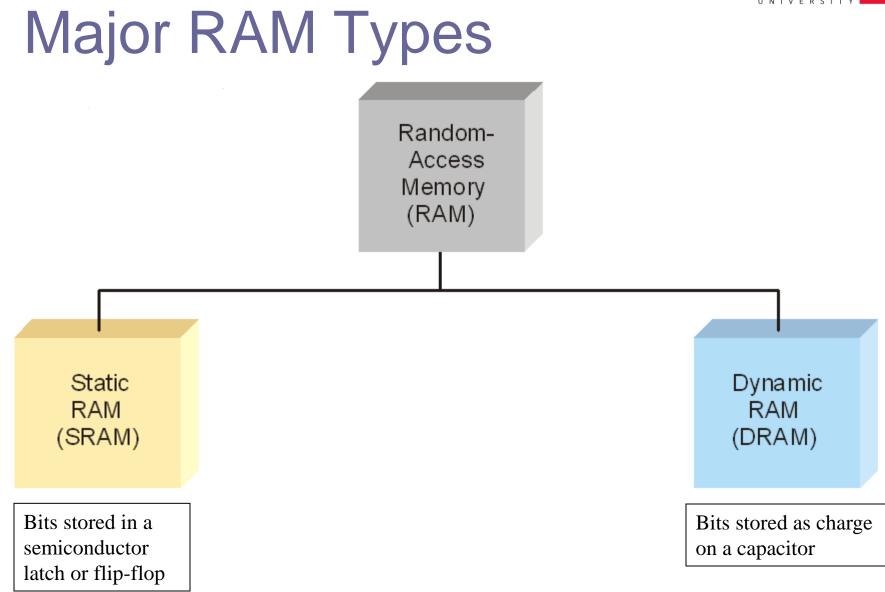

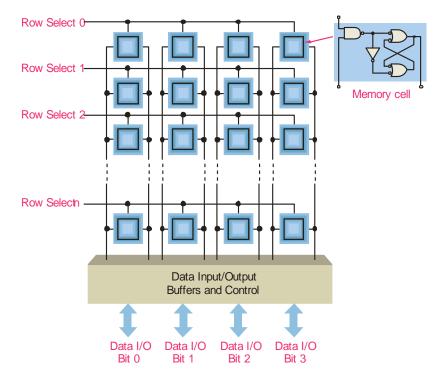

## Static RAM (SRAM)

SRAM uses semiconductor latch memory cells. The cells are organized into an array of rows and columns

SRAM is faster than DRAM but is more complex, takes up more space, and is more expensive. SRAMs are available in many configurations – a typical large SRAM is organized as 512 k X 8 bits

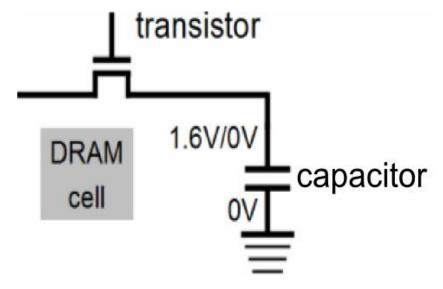

# Dynamic RAM (DRAM)

Dynamic RAMs (DRAMs) store data bits as a charge on a capacitor.

DRAMs are simple and cost effective, but require refresh circuitry to prevent losing data

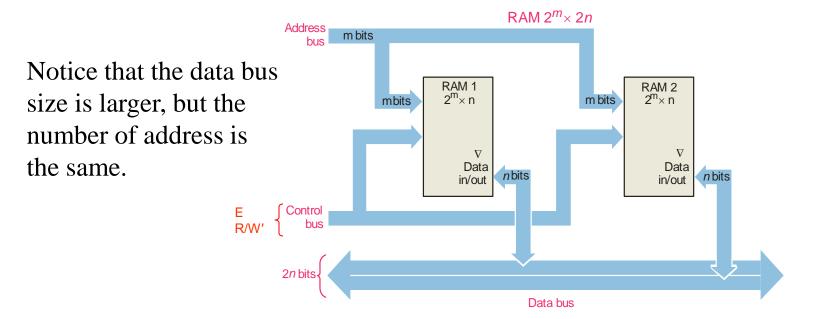

## Memory Expansion (1/2)

Memory can be expanded in either word size or word capacity or both.

To expand word size:

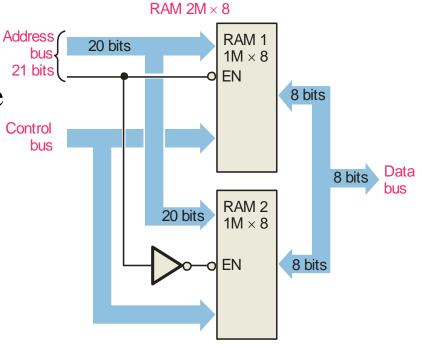

#### Memory Expansion (2/2)

To expand word capacity, you need to add an address line as shown in this example

Notice that the data bus size does not change

### SIMMs and DIMMs

SIMMs (single in-line memory modules) and DIMMs (dual in-line memory modules) are plug-in circuit boards containing the ICs and I/O brought out on edge connectors. SIMMs have a 32-bit data path with I/O on only one side whereas DIMMs have a 64-bit data path with I/O on both sides of the board.

#### References

- Lecture Notes of Dr. Sebastian Magierowski Fall 2013

- "Digital Design (3<sup>rd</sup> and 4<sup>th</sup> Editions)", Morris Mano, Prentice Hall, (2002/2007)

- "Digital Fundamentals (10<sup>th</sup> Edition)", Thomas L. Floyd, Prentice Hall, 2010

- http://ece.gmu.edu/coursewebpages/ECE/ECE4 48/S10/