| <b>A</b> | LU Control                                                                 |                  | 84.47 G                 |

|----------|----------------------------------------------------------------------------|------------------|-------------------------|

| -        | ALU used for<br>Load/Store: F = a<br>Branch: F = subtr<br>R-type: F depend | ract             |                         |

|          | ALU control                                                                | Function         | ā                       |

|          | 0000                                                                       | AND              | ā                       |

|          | 0001                                                                       | OR               | 1                       |

|          | 0010                                                                       | add              |                         |

|          | 0110                                                                       | subtract         |                         |

|          | 0111                                                                       | set-on-less-than | ]                       |

|          | 1100                                                                       | NOR              |                         |

| M        | <                                                                          | Chapter 4 — T    | -<br>The Processor — 23 |

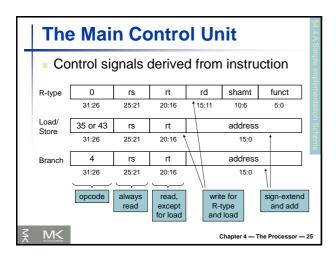

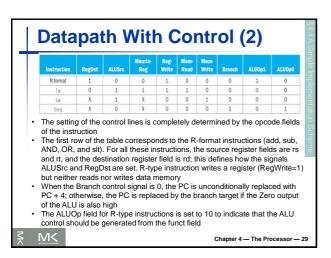

|        |       |                  | •      | ved from<br>s ALU cont | •          |

|--------|-------|------------------|--------|------------------------|------------|

| opcode | ALUOp | Operation        | funct  | ALU function           | ALU contro |

| lw     | 00    | load word        | XXXXXX | add                    | 0010       |

| SW     | 00    | store word       | XXXXXX | add                    | 0010       |

| beq    | 01    | branch equal     | XXXXXX | subtract               | 0110       |

| R-type | 10    | add              | 100000 | add                    | 0010       |

|        |       | subtract         | 100010 | subtract               | 0110       |

|        |       | AND              | 100100 | AND                    | 0000       |

|        |       | OR               | 100101 | OR                     | 0001       |

|        |       | set-on-less-than | 101010 | set-on-less-than       | 0111       |

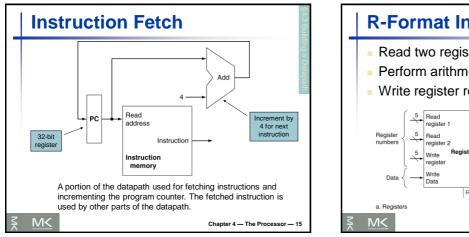

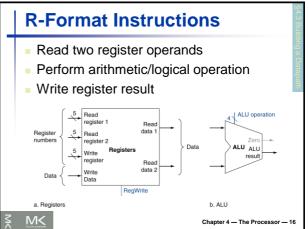

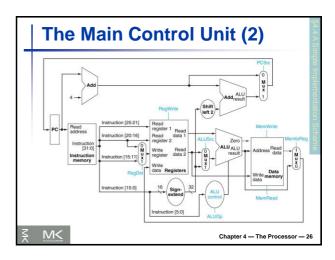

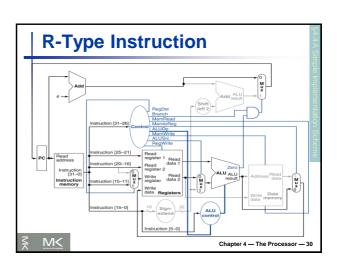

## **R-Type Instruction (2)** \$t1, \$t2,\$t3 For example, add Four steps to execute the instruction in one clock cycle 1. The instruction is fetched, and the PC is incremented 2. Registers \$t2 and \$t3 are read from the register file. Also, the main control unit computes the setting of the control lines during this step 3. The ALU operates on the data read from the register file, using the function code (bits 5:0, funct field) to generate the ALU function 4. The result from the ALU is written into the register file using bits 15:11 of the instruction to select the destination register (\$t1) M< Chapter 4 — The Processor — 31

Chapter 4 — The Processor — 33