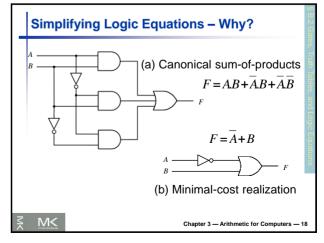

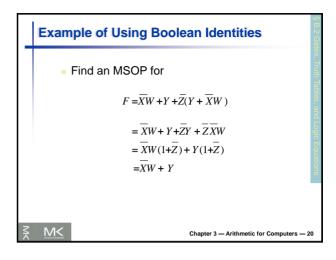

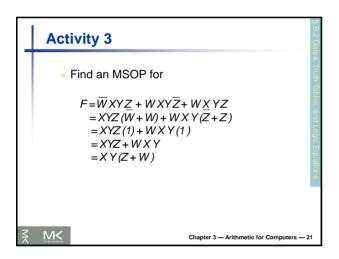

### Simplifying Logic Equations Simplifying logic expressions can lead to using smaller number of gates (parts) to implement the logic expression Can be done using Boolean Identities (algebraic) Karnaugh Maps (graphical) A minimum SOP (MSOP) expression is one that has no more AND terms or variables than any other equivalent SOP expression. A minimum POS (MPOS) expression is one that has no more OR factors or variables than any other equivalent POS expression.

Chapter 3 — Arithmetic for Computers — 19

There may be several MSOPs of an expression

###

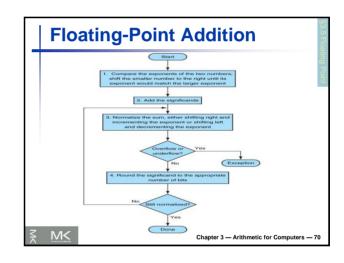

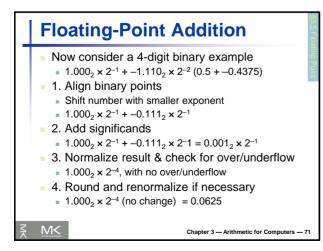

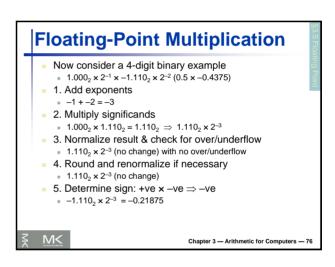

# Floating-Point Addition Consider a 4-digit decimal example 9.999 × 10¹ + 1.610 × 10⁻¹ 1. Align decimal points Shift number with smaller exponent 9.999 × 10¹ + 0.016 × 10¹ 2. Add significands 9.999 × 10¹ + 0.016 × 10¹ = 10.015 × 10¹ 3. Normalize result & check for over/underflow 1.0015 × 10² 4. Round and renormalize if necessary 1.002 × 10²

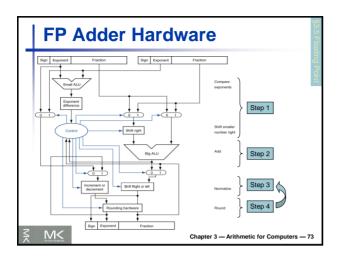

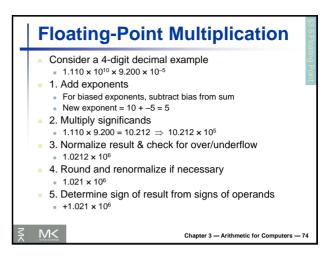

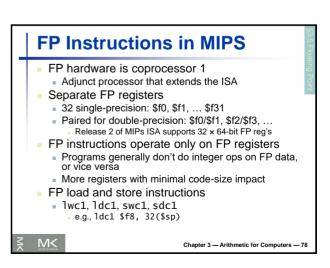

# FP Arithmetic Hardware FP multiplier is of similar complexity to FP adder But uses a multiplier for significands instead of an adder FP arithmetic hardware usually does Addition, subtraction, multiplication, division, reciprocal, square-root FP ↔ integer conversion Operations usually take several cycles Can be pipelined

# FP Instructions in MIPS Single-precision arithmetic add.s, sub.s, mul.s, div.s e.g., add.s \$f0, \$f1, \$f6 Double-precision arithmetic add.d, sub.d, mul.d, div.d e.g., mul.d \$f4, \$f4, \$f6 Single- and double-precision comparison c.xx.s, c.xx.d (xx is eq, lt, le, ...) Sets or clears FP condition-code bit e.g. c.lt.s \$f3, \$f4 Branch on FP condition code true or false bclt, bclf e.g., bclt TargetLabel

## Right Shift and Division ■ Left shift by *i* places multiplies an integer by 2<sup>i</sup> ■ Right shift divides by 2<sup>i</sup>? ■ Only for unsigned integers ■ For signed integers ■ Arithmetic right shift: replicate the sign bit ■ e.g., -5 / 4 ■ 11111011<sub>2</sub> >> 2 = 11111110<sub>2</sub> = -2 ■ Rounds toward -∞ ■ c.f. 11111011<sub>2</sub> >>> 2 = 00111110<sub>2</sub> = +62