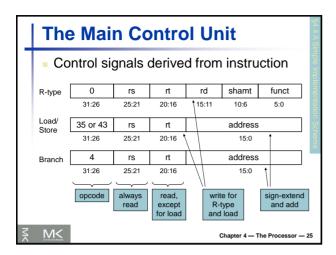

| A   | LU Control                                                                 |                  | §4.4 A Si             |

|-----|----------------------------------------------------------------------------|------------------|-----------------------|

|     | ALU used for<br>Load/Store: F = a<br>Branch: F = subtr<br>R-type: F depend | act              | mple Implementation S |

|     | ALU control                                                                | Function         | - Chen                |

|     | 0000                                                                       | AND              | пе                    |

|     | 0001                                                                       | OR               |                       |

|     | 0010                                                                       | add              |                       |

|     | 0110                                                                       | subtract         |                       |

|     | 0111                                                                       | set-on-less-than |                       |

|     | 1100                                                                       | NOR              |                       |

| < M | <                                                                          | Chapter 4 — T    | he Processor — 23     |

|        |       | -bit ALUC<br>tional logic | -      |                  | -           |

|--------|-------|---------------------------|--------|------------------|-------------|

| opcode | ALUOp | Operation                 | funct  | ALU function     | ALU control |

| lw     | 00    | load word                 | XXXXXX | add              | 0010        |

| SW     | 00    | store word                | XXXXXX | add              | 0010        |

| beq    | 01    | branch equal              | XXXXXX | subtract         | 0110        |

| R-type | 10    | add                       | 100000 | add              | 0010        |

|        |       | subtract                  | 100010 | subtract         | 0110        |

|        |       | AND                       | 100100 | AND              | 0000        |

|        |       | OR                        | 100101 | OR               | 0001        |

|        |       | set-on-less-than          | 101010 | set-on-less-than | 0111        |

Chapter 4 — The Processor — 31

. Σ Μ< <image>