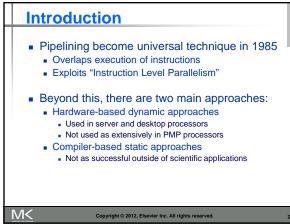

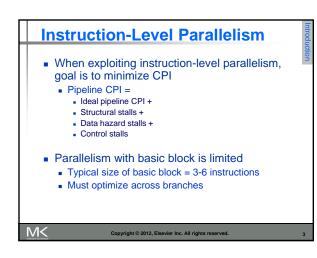

| M< | Computer Architecture<br>A Quantitative Approach, Fifth Edition |

|----|-----------------------------------------------------------------|

|    | Chapter 3                                                       |

|    | Instruction-Level Parallelism<br>and Its Exploitation           |

|    |                                                                 |

| M< | Copyright © 2012, Elsevier Inc. All rights reserved.            |

| Data D | ependei                              | nce                                                         |   |

|--------|--------------------------------------|-------------------------------------------------------------|---|

| Loop:  | L.D<br>ADD.D<br>S.D<br>DADDUI<br>BNE | F0,0(R1)<br>F4,F0,F2<br>F4,0(R1)<br>R1,R1,#-8<br>R1,R2,Loop |   |

| M<     | Copyright © 2012,                    | Elsevier Inc. All rights reserved.                          | 9 |

| Exam                                                            | ples                                                           |                                                                                                                                                                       | Introduction |  |

|-----------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|

| Example<br>DADDU<br>BEQZ<br>DSUBU<br>L:<br>OR                   | <u>1:</u><br>R1,R2,R3<br>R4,L<br>R1,R1,R6<br>R7,R1,R8          | <ul> <li>OR instruction dependent<br/>on DADDU and DSUBU</li> <li>Preserving the order alone<br/>is not sufficient (must have<br/>the correct value in R1)</li> </ul> | ction        |  |

| Example     DADDU     BEQZ     DSUBU     DADDU     skip:     OR | 2:<br>R1,R2,R3<br>R12,skip<br>R4,R5,R6<br>R5,R4,R9<br>R7,R8,R9 | <ul> <li>Assume R4 isn't used after skip</li> <li>Possible to move DSUBU before the branch</li> </ul>                                                                 |              |  |

| Copyright © 2012, Elsevier Inc. All rights reserved.            |                                                                |                                                                                                                                                                       |              |  |